4-3 Pipelining 流水线数据通路

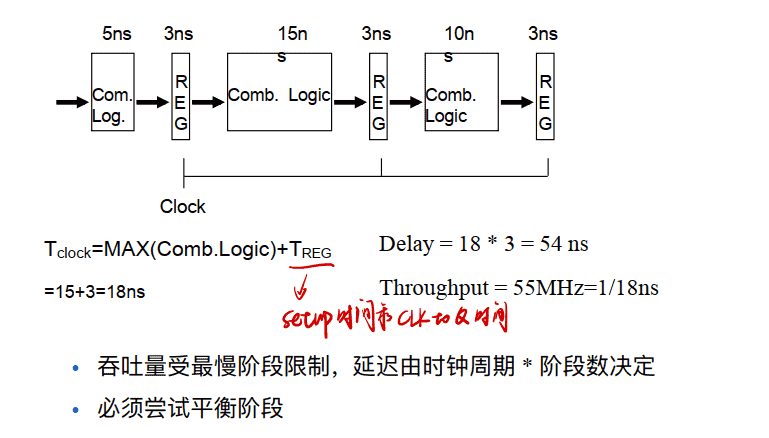

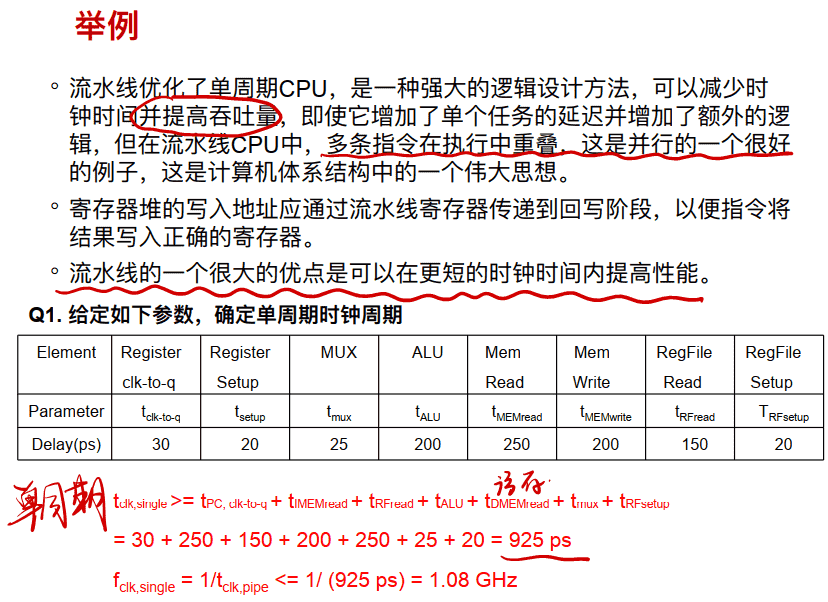

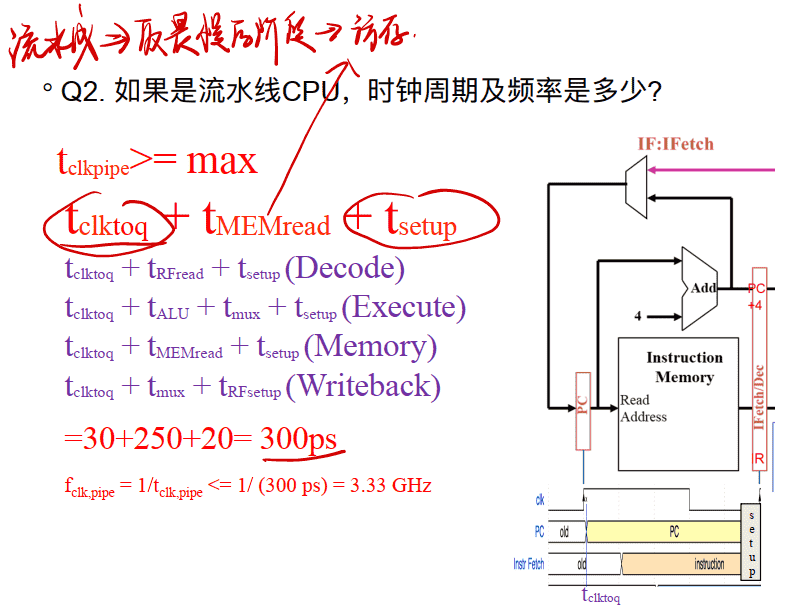

==易错点:流水线的时钟周期除了五个阶段中最长的阶段所需时间外,还有CLK-to-Q time 和 setup time==

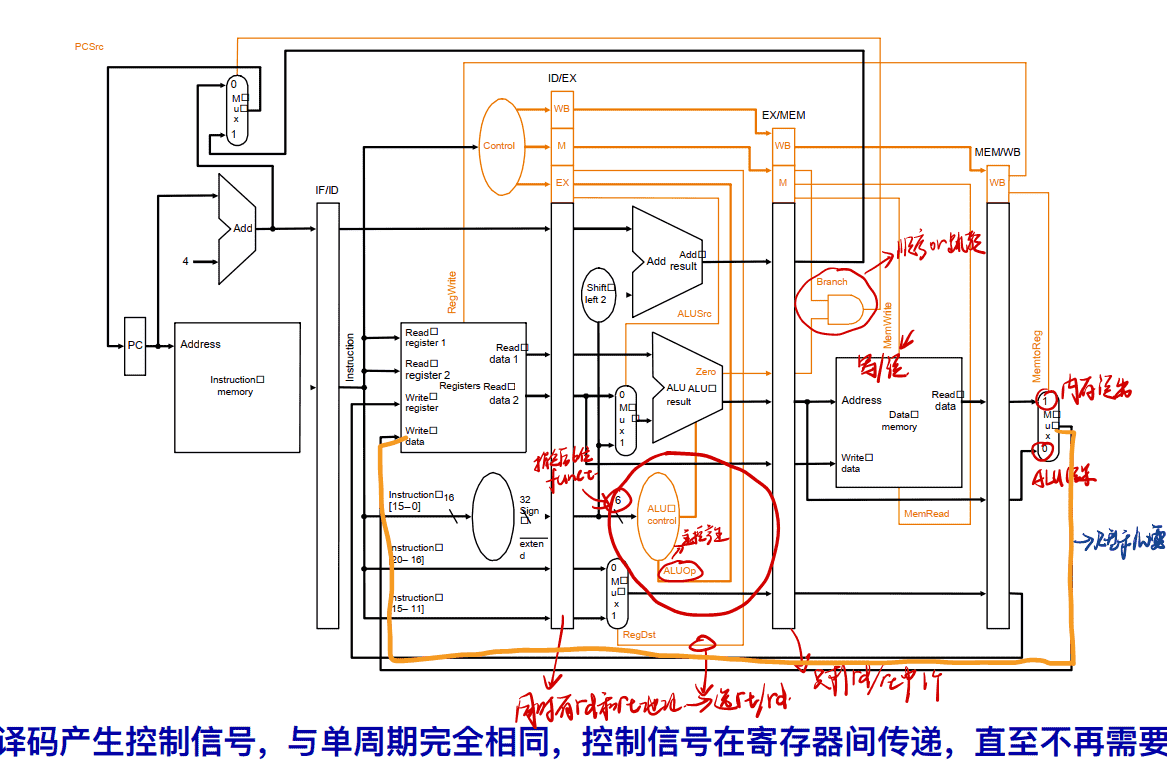

流水线实现简介

数据通路流水线化

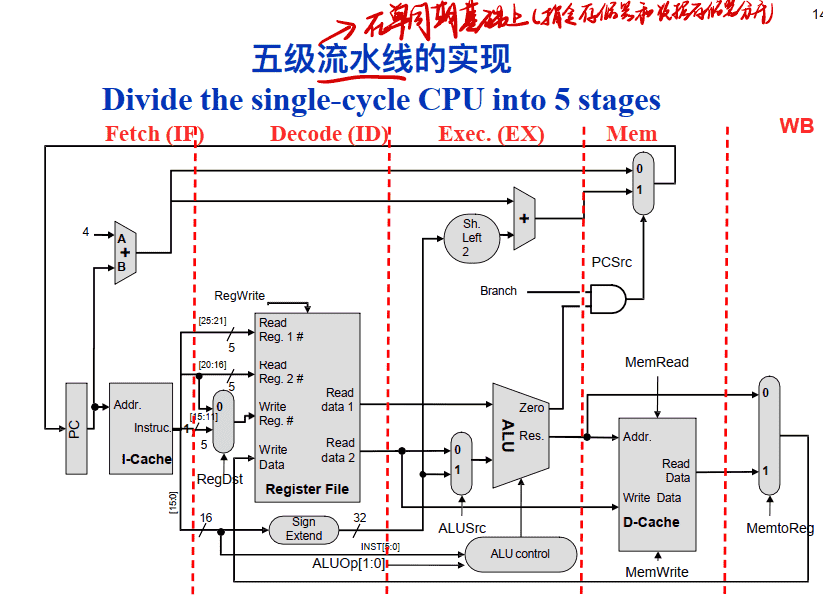

⽬标: 保证(⼏乎) 1.0 的CPI, 同时提⾼时钟速率⽅法: 将处理器转变为⼀个多级流⽔线

- Instruction Fetch IF: 维护 PC. 每周期取⼀个指令.

- Register File(RF/ID): 从寄存器组RF中读取操作数.

- ALU: 执⾏指定的运算.

- Data Access:存储器访问(I type load store指令需要)

- Reg Write-Back(WB): 将结果写回到寄存器

R型指令的四级流水线:IF -> ID -> ALU -> WB

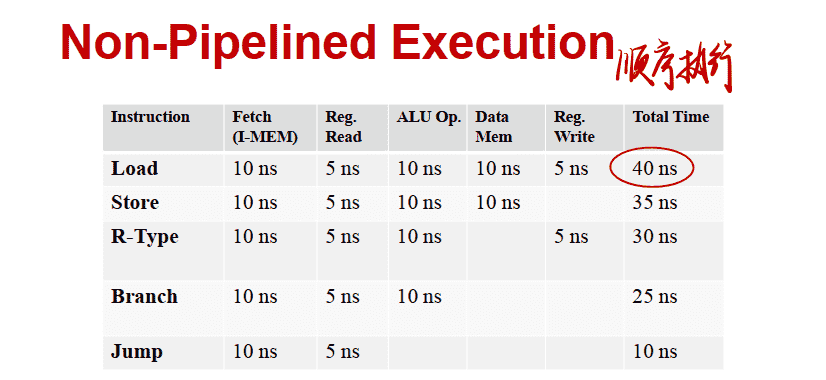

Non-Pipelined Execution

注意每种指令所需阶段

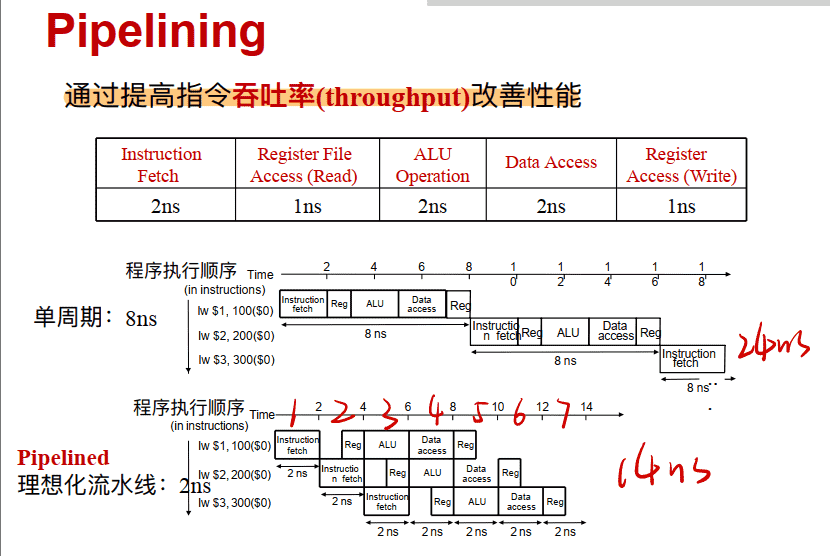

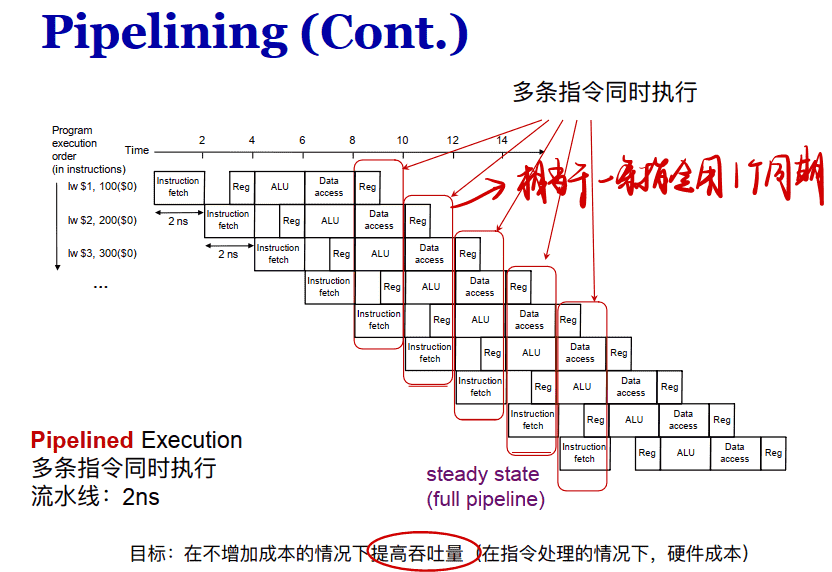

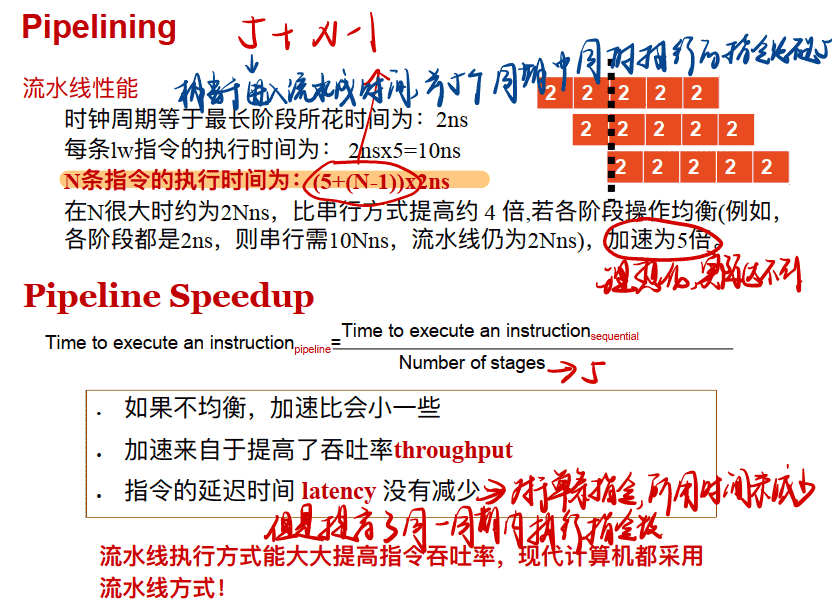

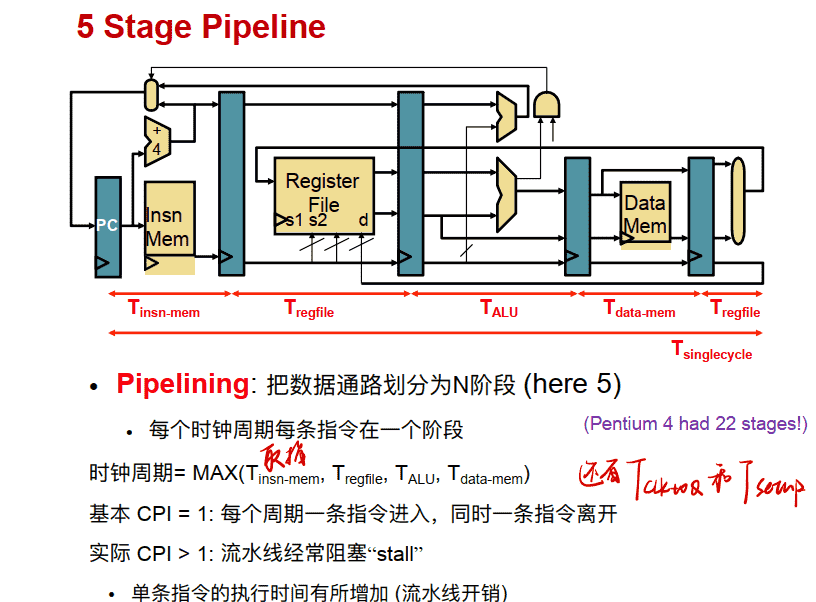

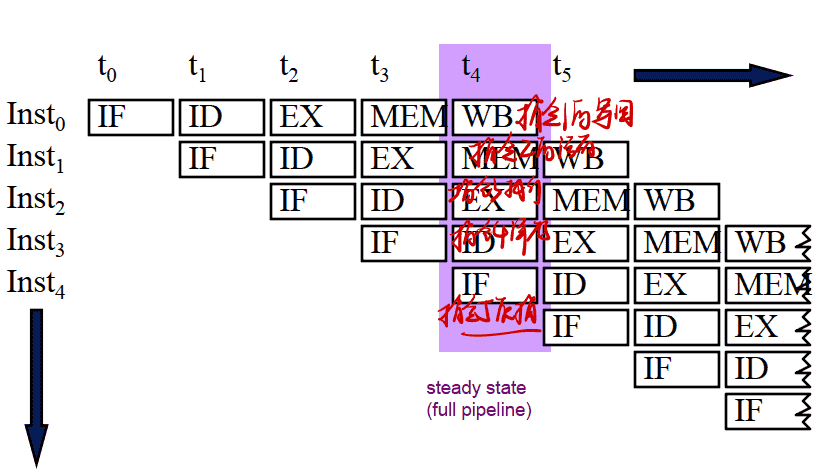

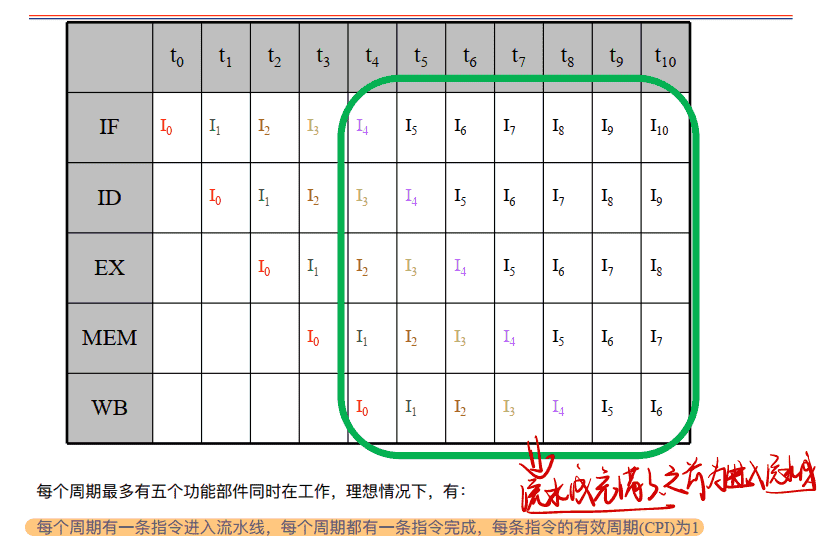

Pipelining

通过提⾼指令吞吐率(throughput)改善性能

==N条指令所需的阶段数:5+N-1=4+N==

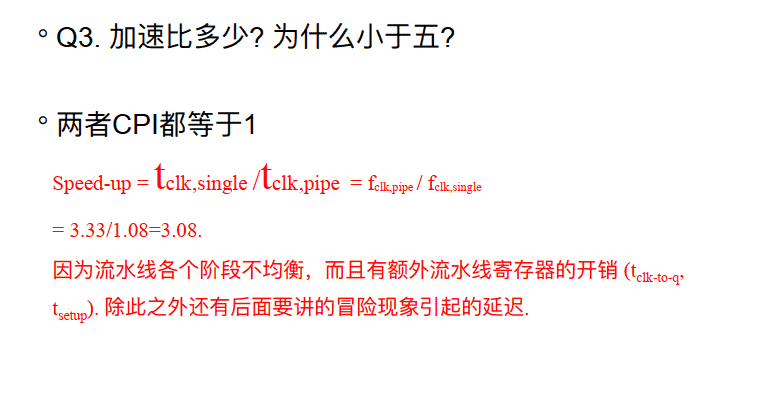

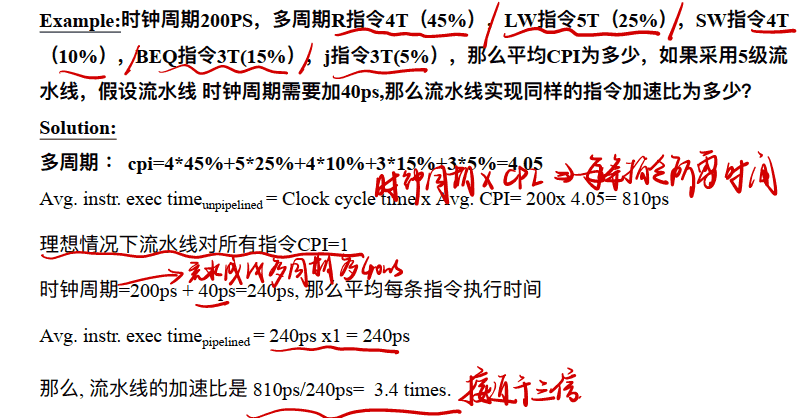

Pipelining Performance (与多周期比)

多周期数据通路需要知道每种指令的比例,多周期时钟周期选用5个阶段中最长的一个

五级流水线的实现(单周期)

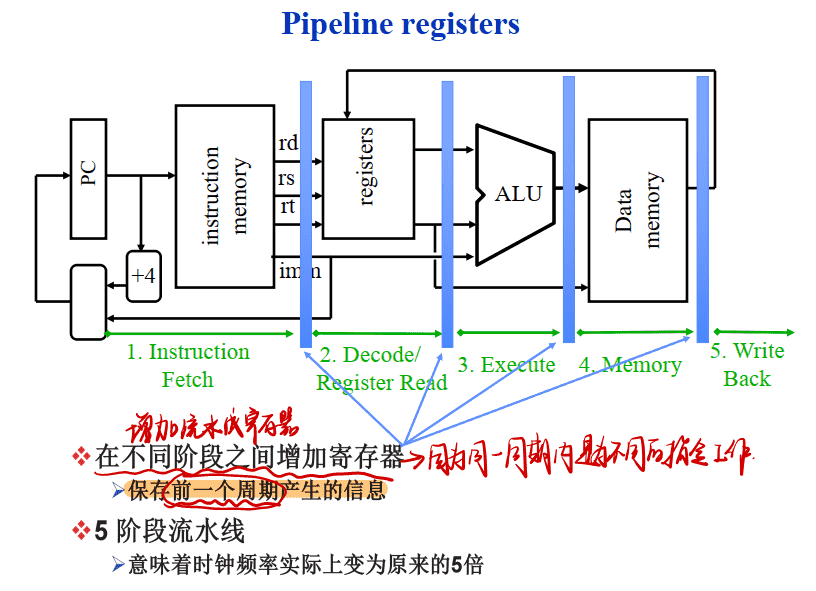

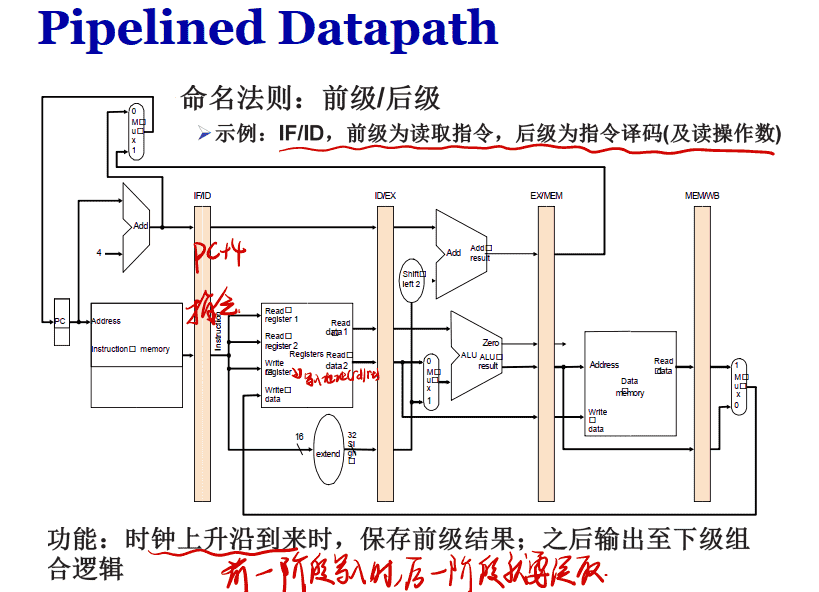

Pipeline registers

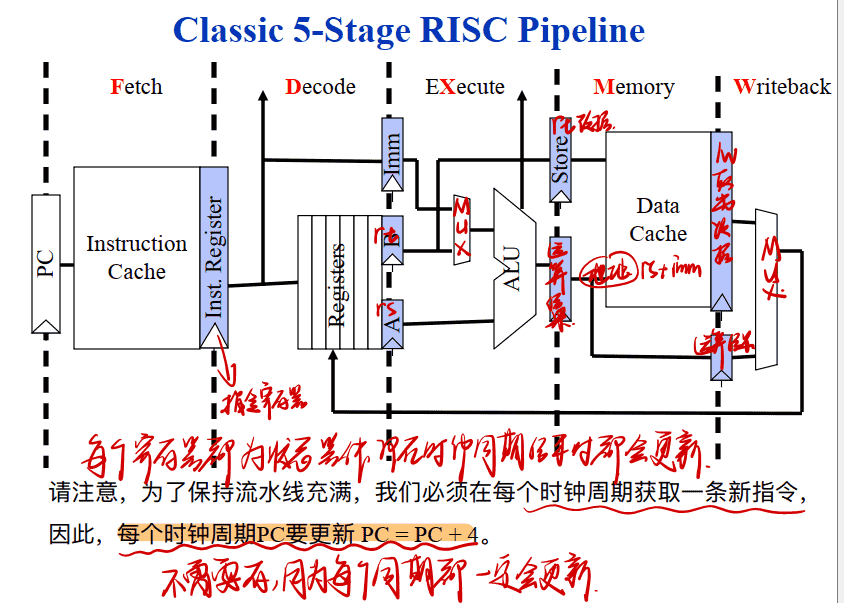

Classic 5-Stage RISC Pipeline

Nonuniform Pipelining非均匀流水线

==时钟周期除了五个阶段的时间外,还需要CLK-to-Q Time and Setup Time==

流水线操作说明

操作视角

资源视角

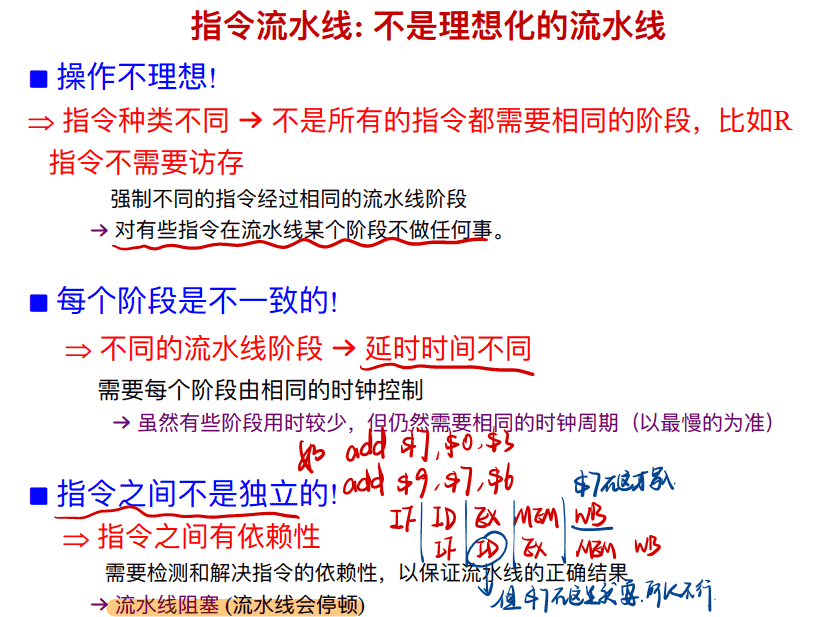

指令流水线: 不是理想化的流水线

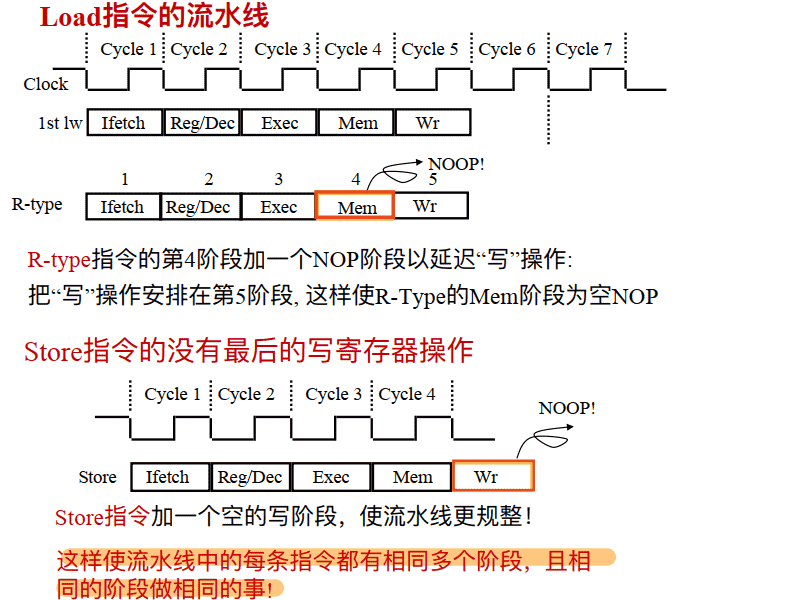

NOP阶段即为空阶段,什么都不做,只是为了延迟写操作,使得条指令都是五个状态

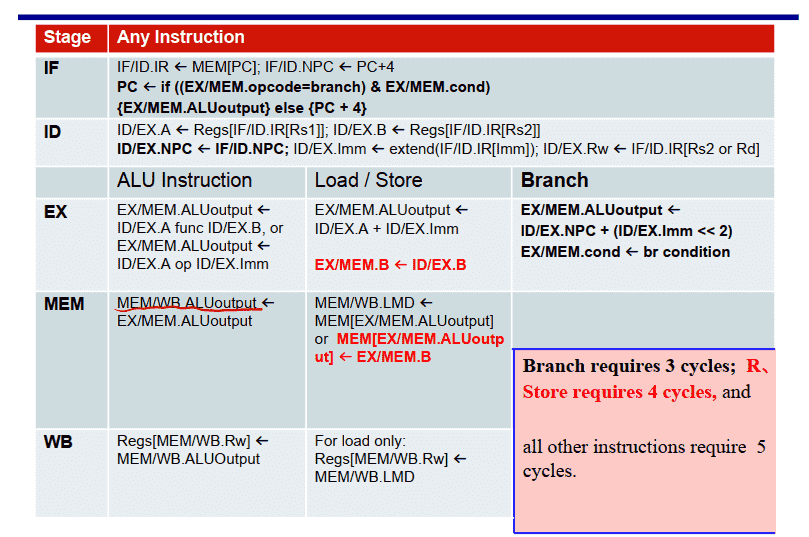

五个阶段的操作

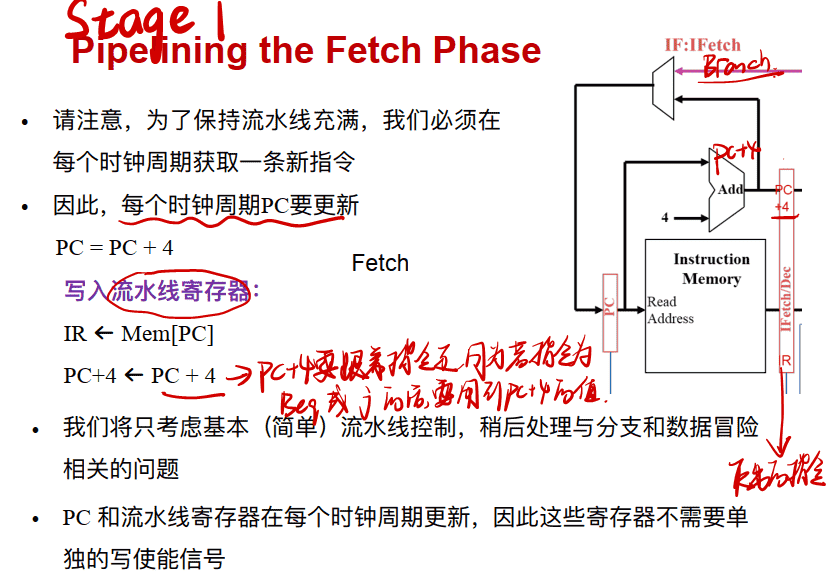

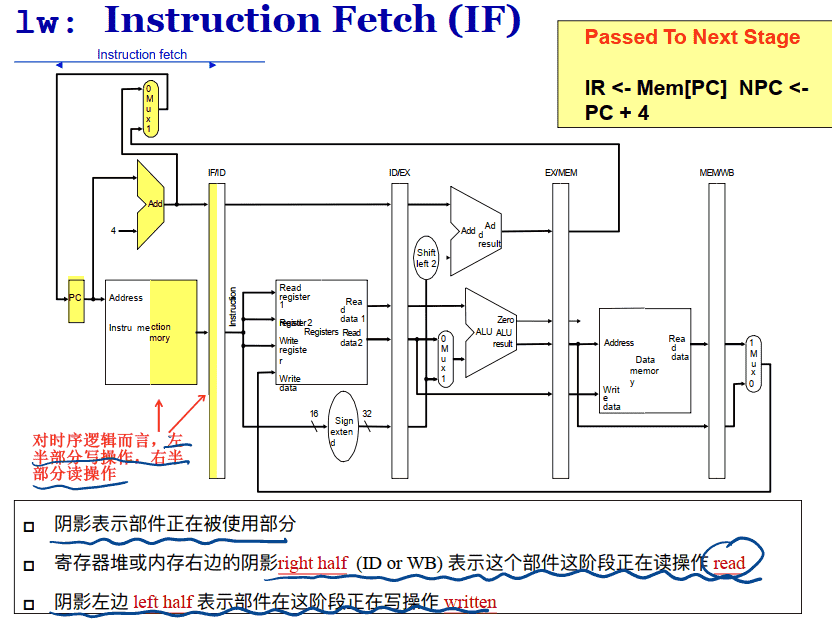

Stage 1 Pipelining the Fetch Phase

流水线寄存器IF/ID中数据:

- PC+4

- 取出的指令

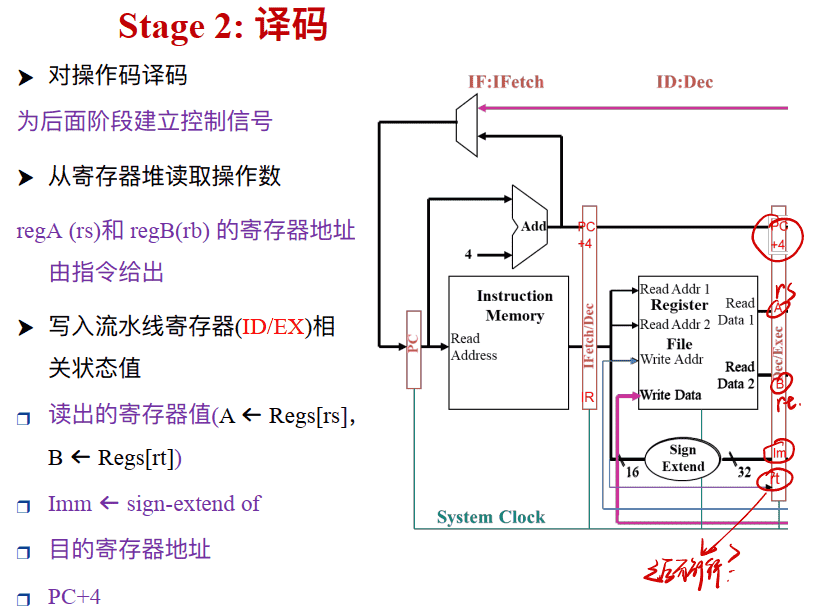

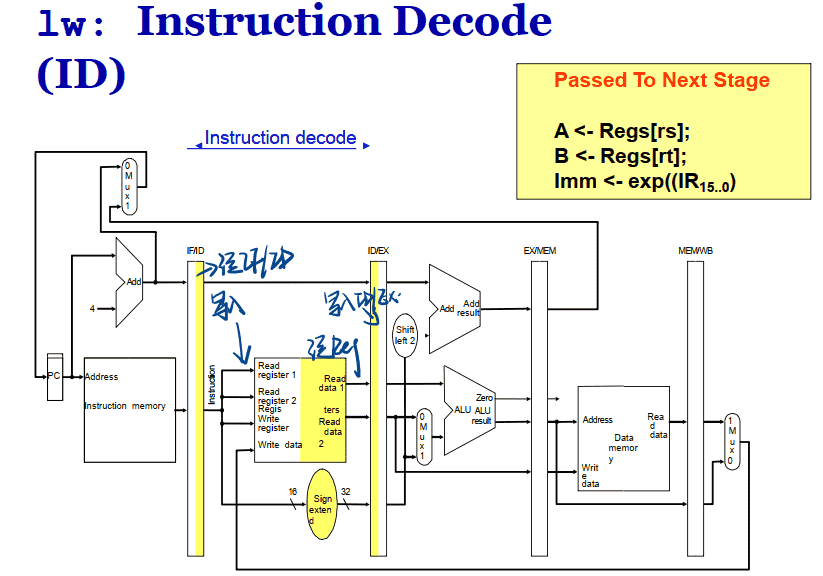

Stage 2: 译码

流水线寄存器ID/EX中数据:

-

PC+4

-

A(rs的内容)

-

B(rt的内容)

-

imm

-

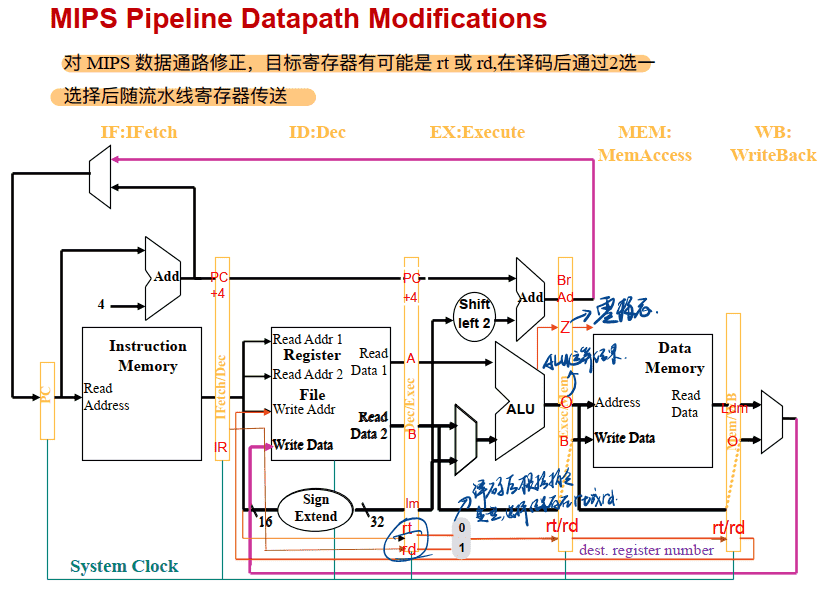

目的寄存器地址(rs和rd的地址,因为还没有译码得出是何种指令,不知道write back的寄存器是rt还是rd)

-

控制信号

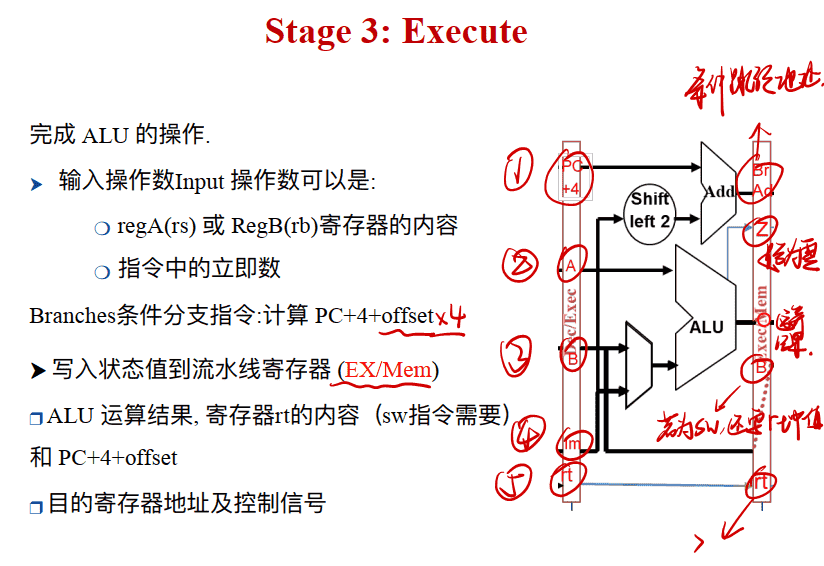

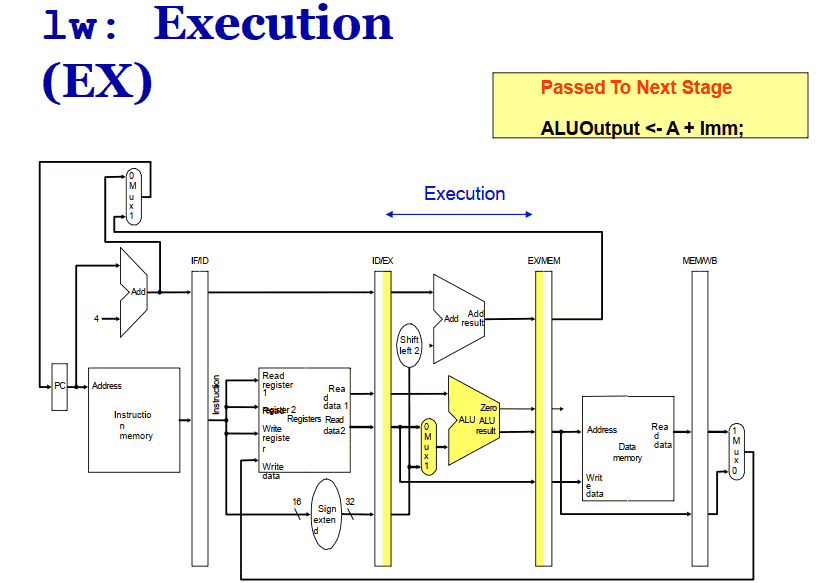

Stage 3: Execute

在此完成条件分支地址的计算

流水线寄存器EX/MEM中数据:

- ALU运算结果

- B(rt的内容,sw指令需要)

- PC+4+offset(branch需要)

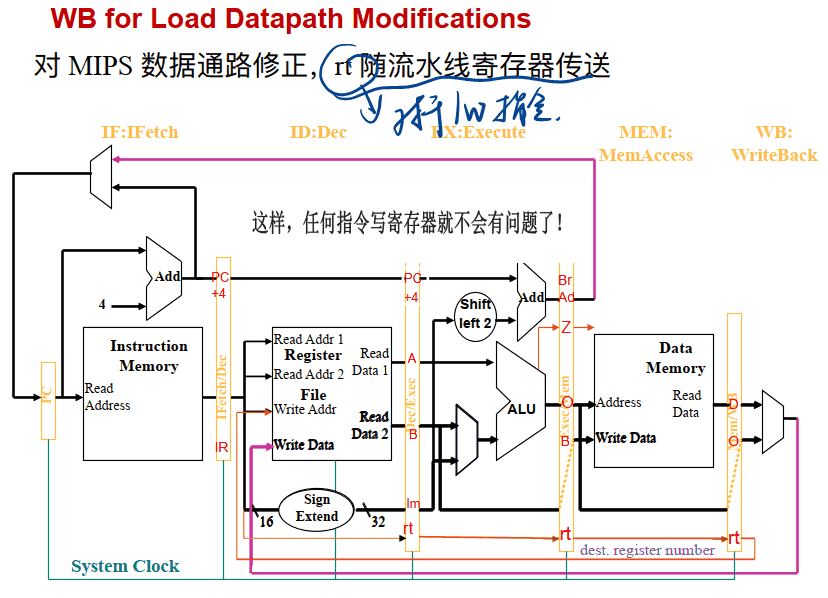

- 目的寄存器地址(此时译码完毕,知道是何种指令了,所以这里只存rt和rd中其中一个的地址)

- 控制信号

回顾多周期

多周期的PC+4在IF阶段计算,与流水线一样,但是多周期的条件分支跳转地址是在译码阶段ID就完成了,ALU运算阶段只需计算A和B的值,然后决定是否将分支地址写入PC

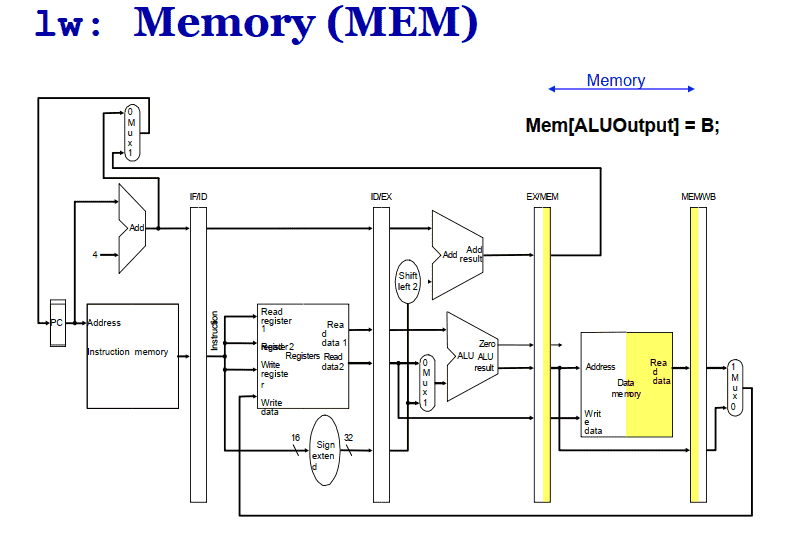

Stage 4: Memory Operation

- 内存访问(lw/sw指令) ❒ ALU 结果包含 lw 和 sw的访问地址 ❒ 控制信号包含内存访问的读写信号

- 写状态值到下⼀级流⽔线寄存器 (Mem/WB) ❒ ALU 结果或内存读取的数据 ❒ ⽬的及寄存器地址及控制信号等

流水线寄存器MEM/WB中数据:

- ALU计算结果 or 内存中取出来的值

- 目的寄存器地址(rt和rd中一个)

- 控制信号。

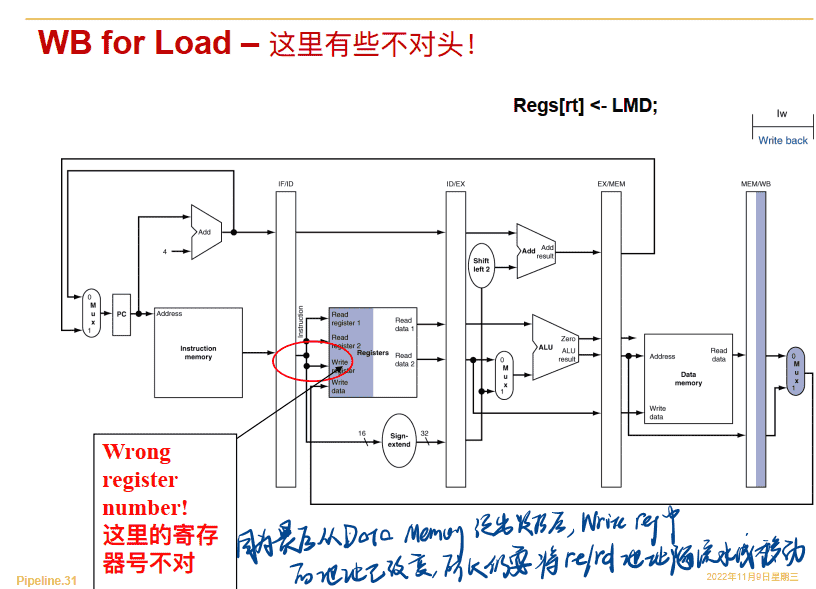

Stage 5: Write back

- 结果写⼊寄存器堆 (if required) ❒ 写内存读取数据到⽬的寄存器 (rt)(对于lw 指令) ❒ 写 ALU 结果到⽬的寄存器(rd/rt)(对于运算指令) ❒ 控制信号(寄存器写使能等)

流水线各阶段操作细节

3周期:条件分支branch

4周期:R型,sw

5周期:其他全部

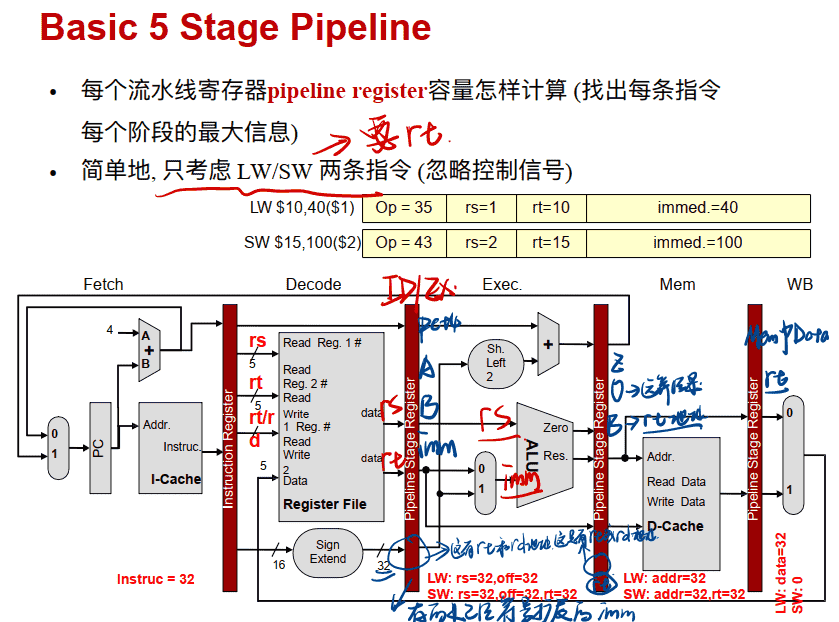

Basic 5 Stage Pipeline

以下的图仍有要修正的地方:目的寄存器地址的来源

lw: Instruction Fetch (IF)

lw: Instruction Decode (ID)

lw:Execution (EX)

lw: Memory (MEM)

修正

对 MIPS 数据通路修正,目的寄存器地址随流⽔线寄存器传送

MIPS Pipeline Datapath Modifications

How many bits wide is each pipeline register?

-

PC – 32 bits

-

IF/ID – 64 bits(PC+IR)

PC+4和取出的指令,各32位

-

ID/EX – 9(con) + 32x4 + 10 = 147 rs=32,pc=32,off=32(扩展后imm),rt=32,rt-addr=5,rd-addr=5(A、B、PC+4、扩展后imm、rt和rd地址)

-

EX/MEM – 5(con) + 1 + 32x3 + 5 = 107 zero=1,Aluout=32,Braddr=32,rt=32(rt中数据,sw要用),rt/rd-addr=5

-

MEM/WB – 2(con) + 32x2 + 5 = 71 Ldata=32(lw读出的数据),Aluout=32, rt/rdaddr=5

时钟驱动的流水线时空图

(作业中需要画)

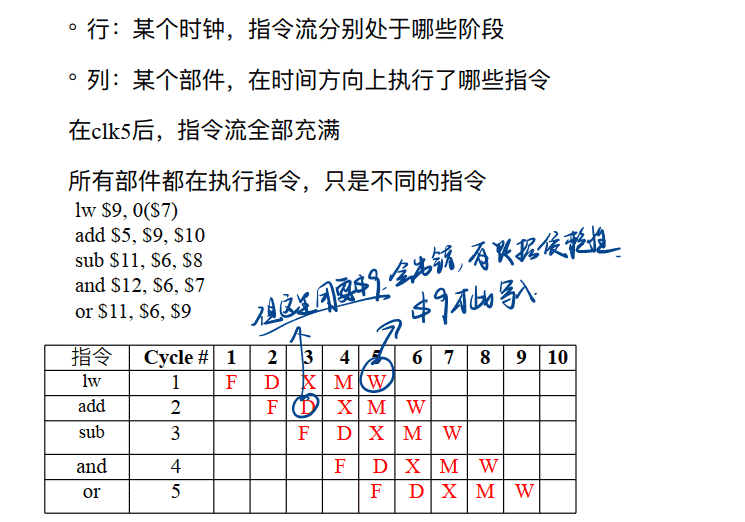

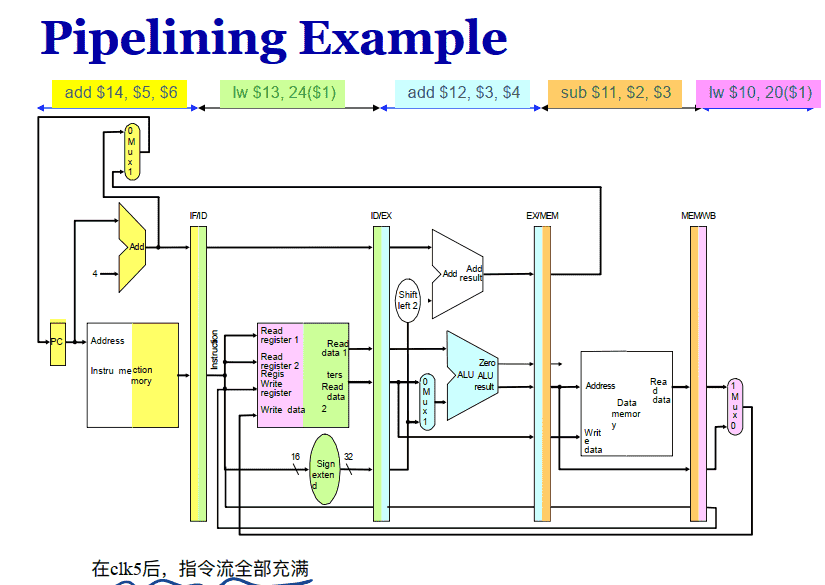

Pipelining Example

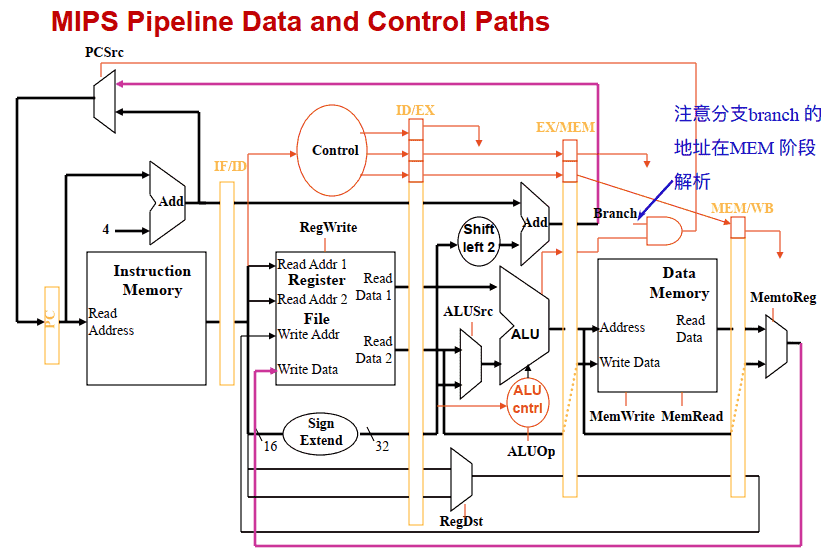

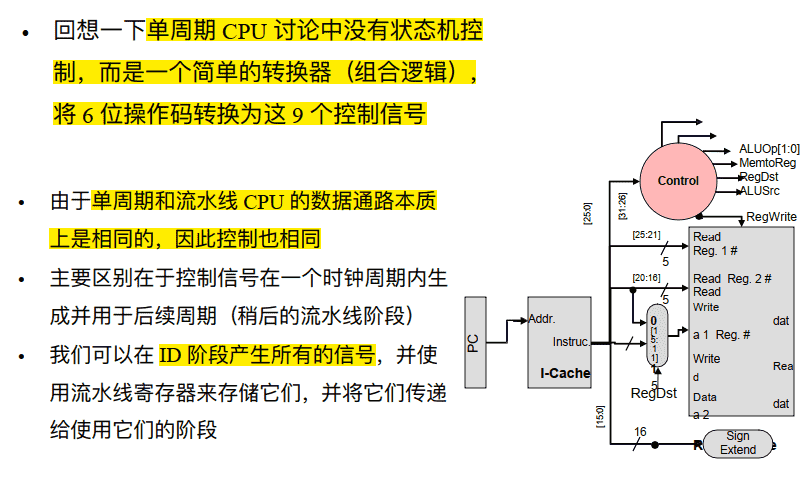

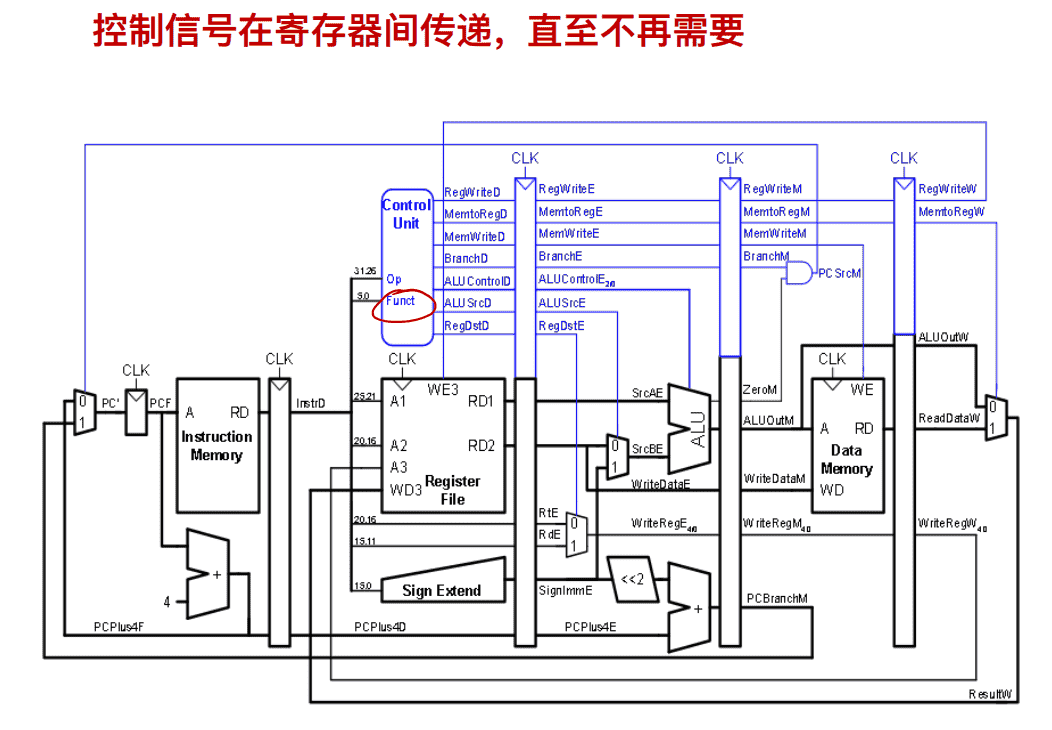

控制信号

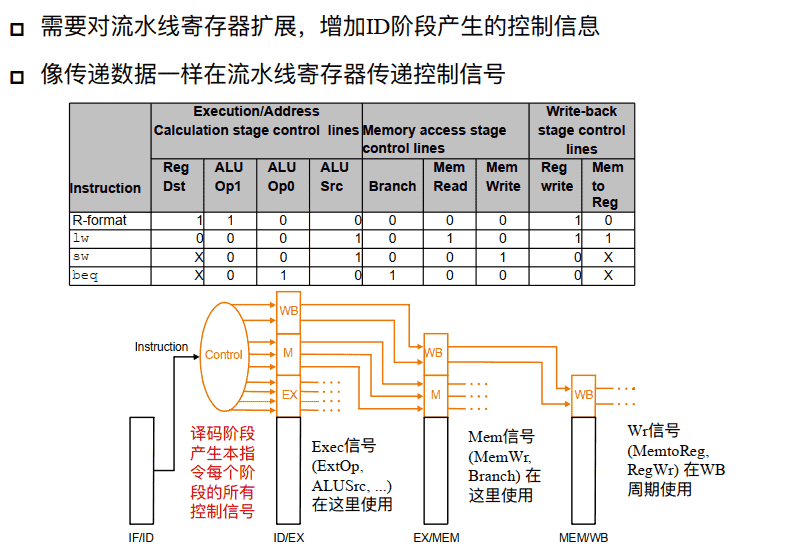

- 控制信号在RF/ID译码阶段产生————由控制逻辑电路译码生成

- 控制信号也必须流⽔线化

- 针对EX阶段的控制信号 ExtOP, ALUSrc等;⼀个时钟周期后⽤到

- 针对Memory的控制信号 MemWr, Branch;两个周期后⽤到

- 针对寄存器回写的控制信号 MemToReg, RegWr等; 三个周期后⽤到

(只有这三个阶段有控制信号)

MIPS Pipeline Data and Control Paths

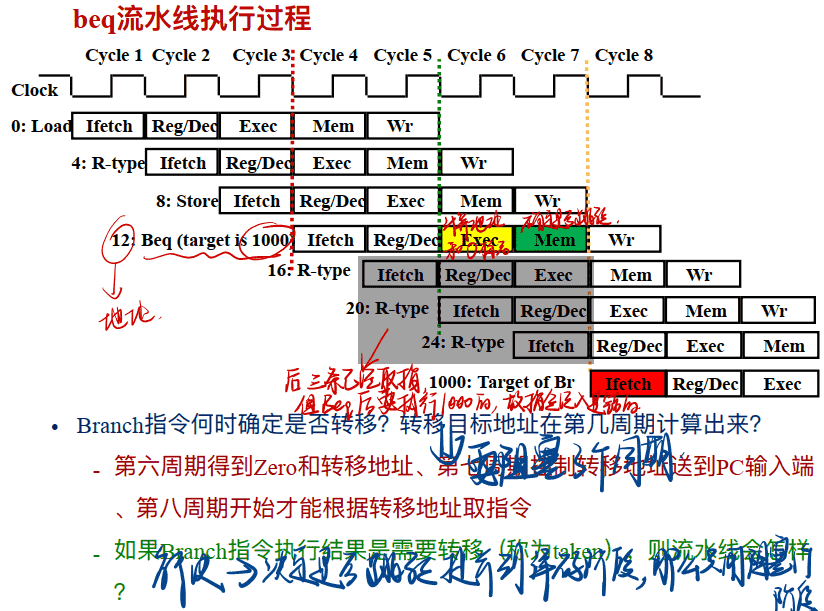

==分支branch地址在MEN阶段解析,在ALU阶段计算==,因为需要branch信号和zero信号与才能判断是否跳转

Control Signal Generation

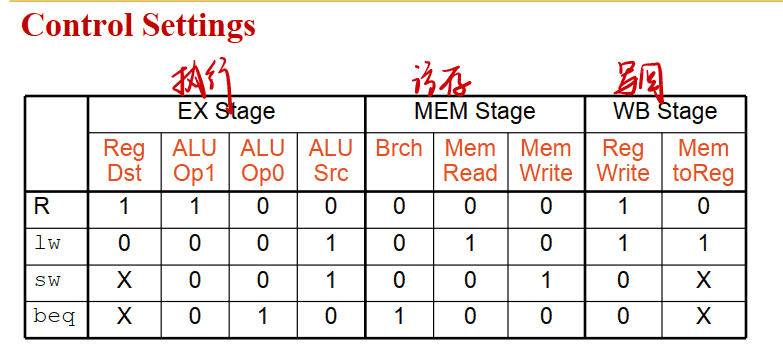

Control Settings

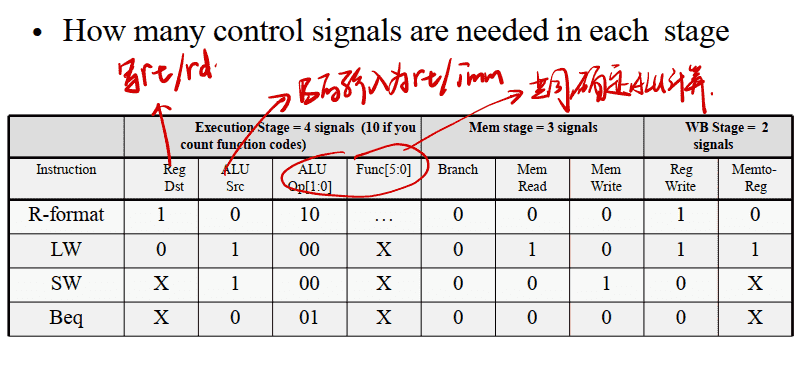

Control Signals per Stage

Pipeline Control

每个阶段 (IF, ID, EX, MEM, WB)需要控制什么?

- IF: 取指 、 PC 递增

- ID: 指令译码和从寄存器堆取操作数/或⽴即数

- EX: Execution stage

- RegDst

- ALUop[1:0]

- ALUSrc

- MEM: Memory stage

- Branch

- MemRead

- MemWrite

- WB: Writeback

- MemtoReg

- RegWrite (注意这个信号在ID阶段的寄存器堆)

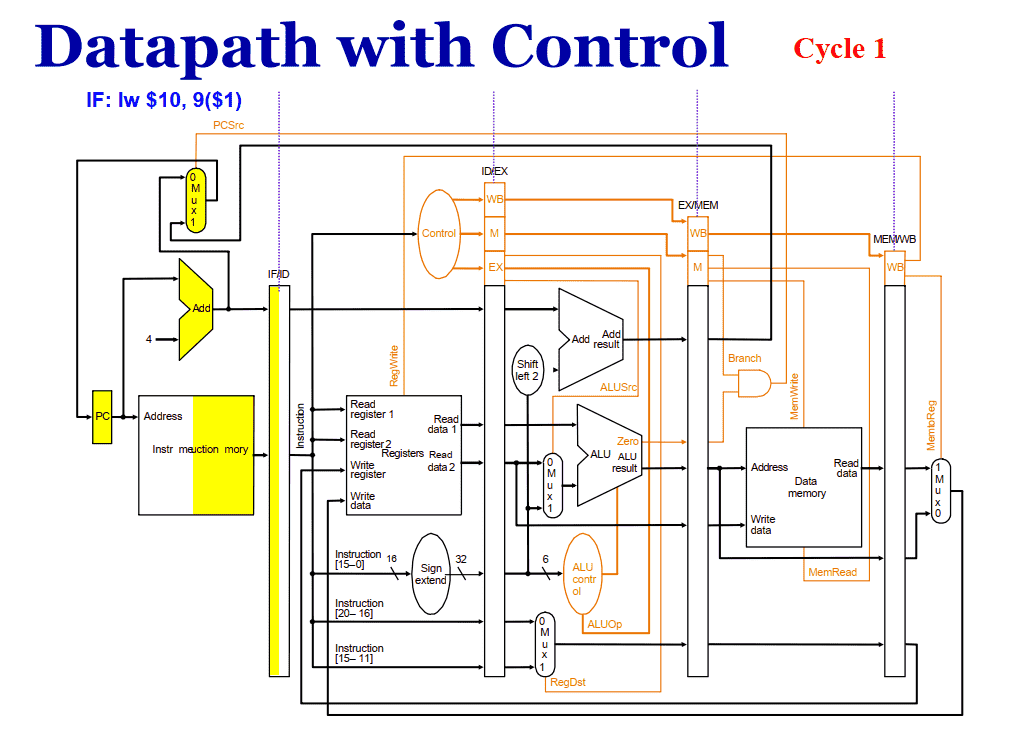

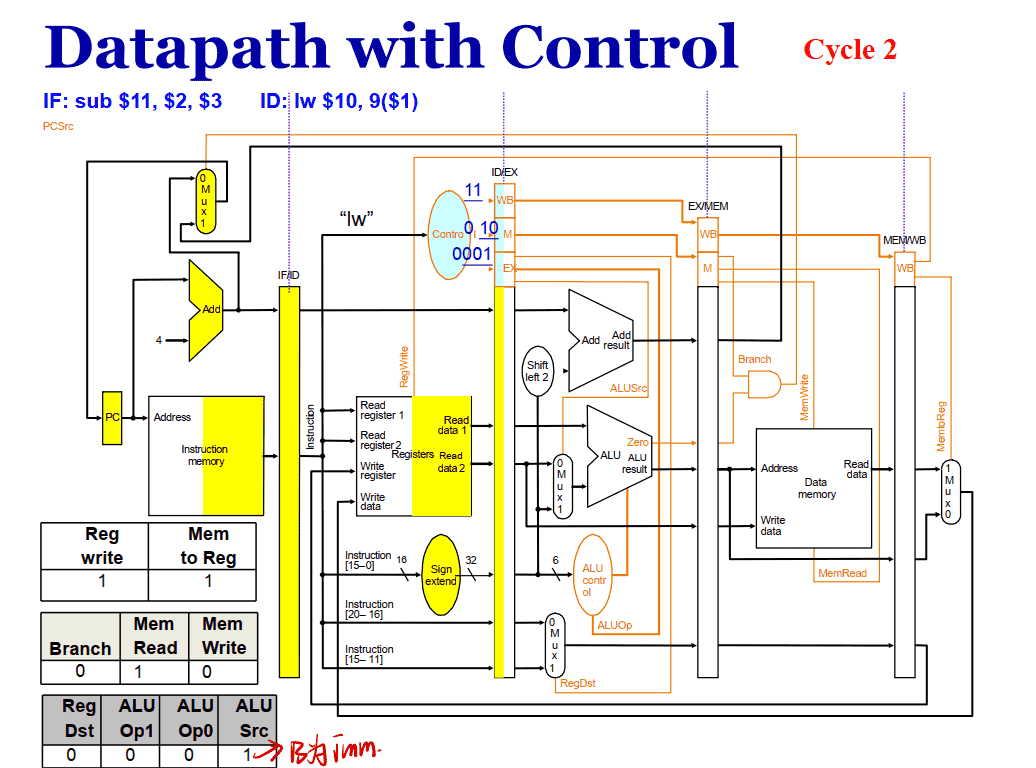

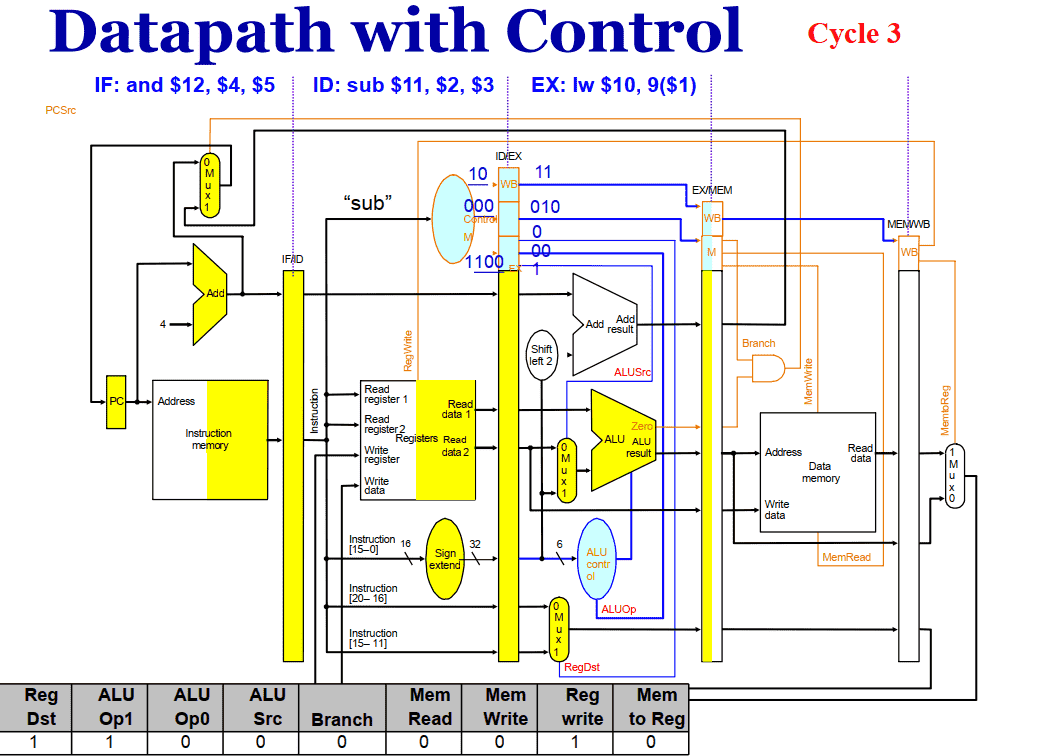

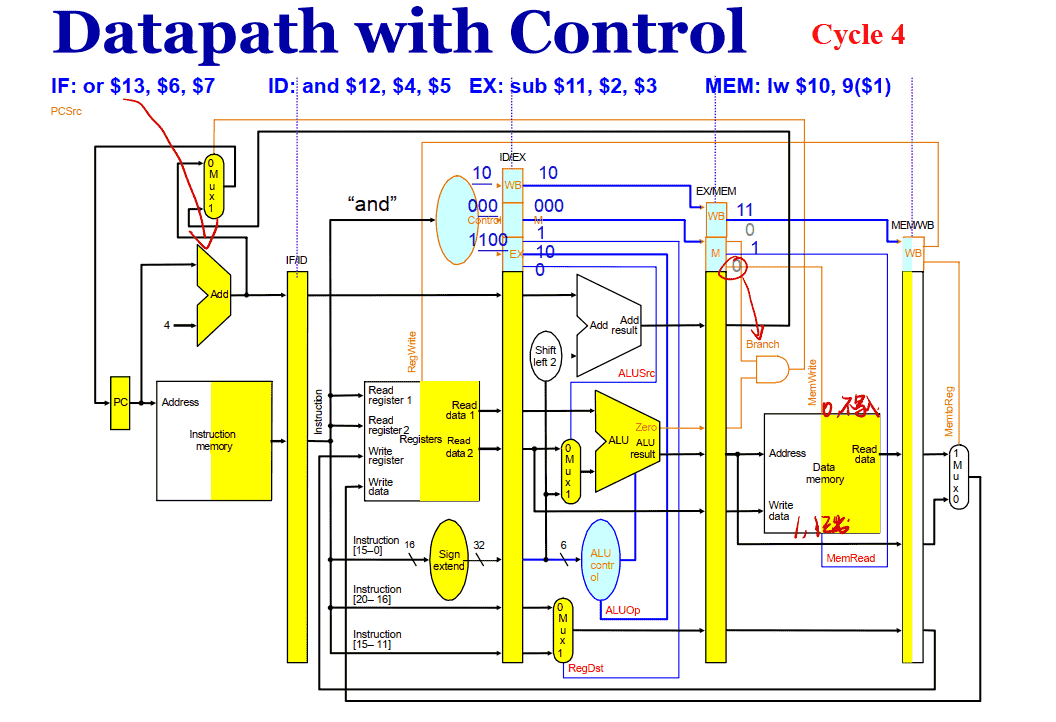

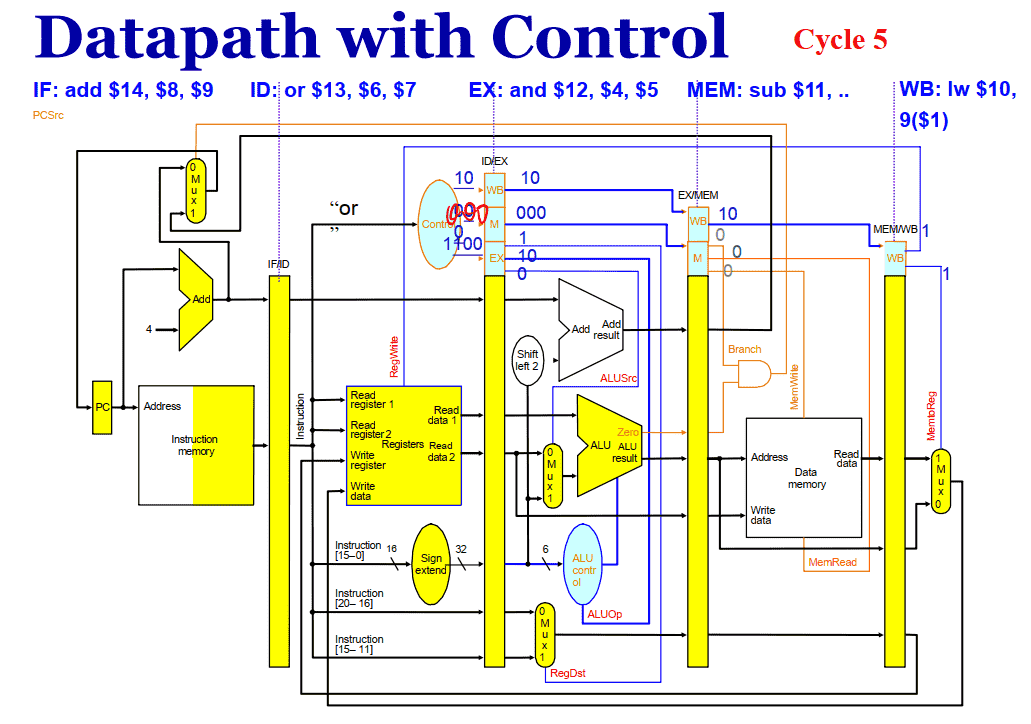

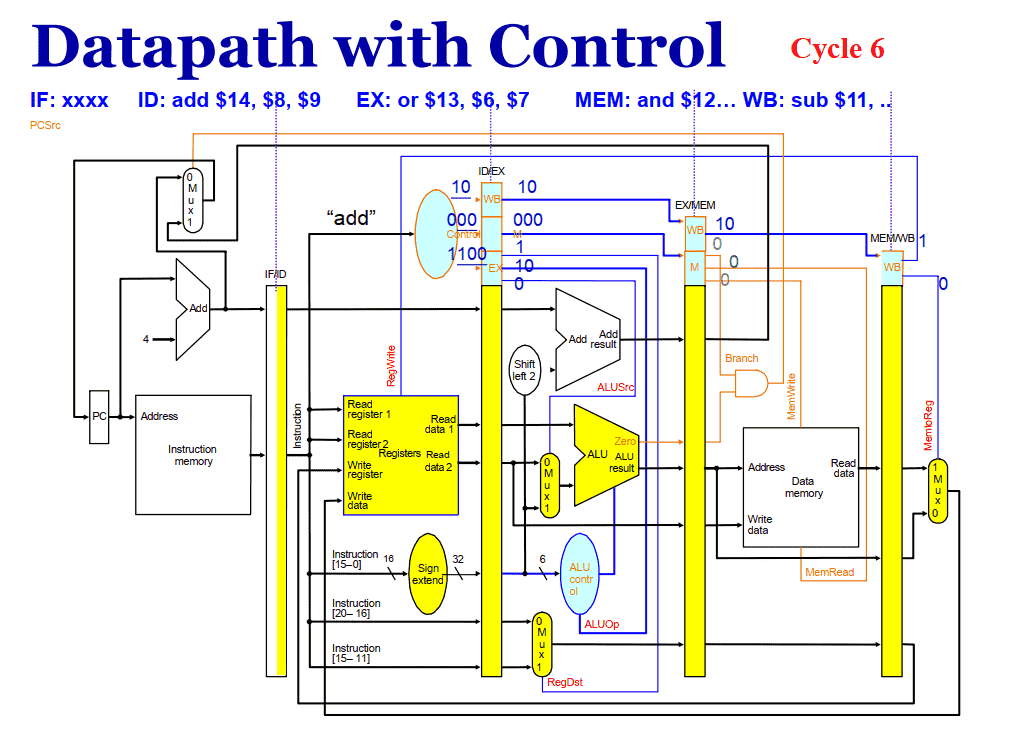

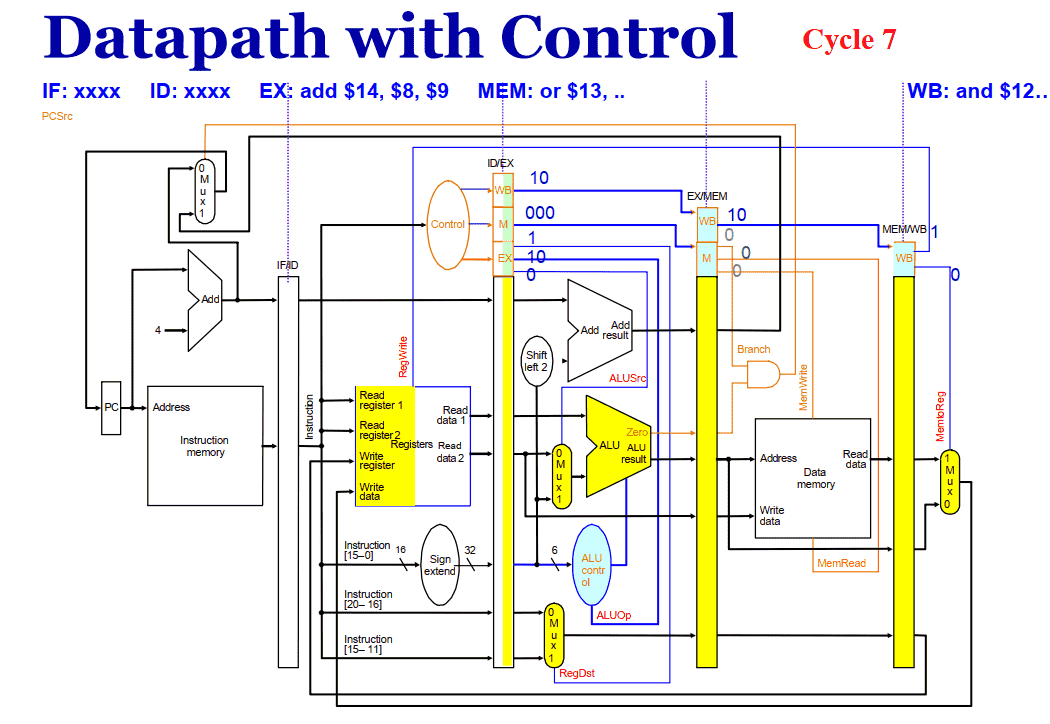

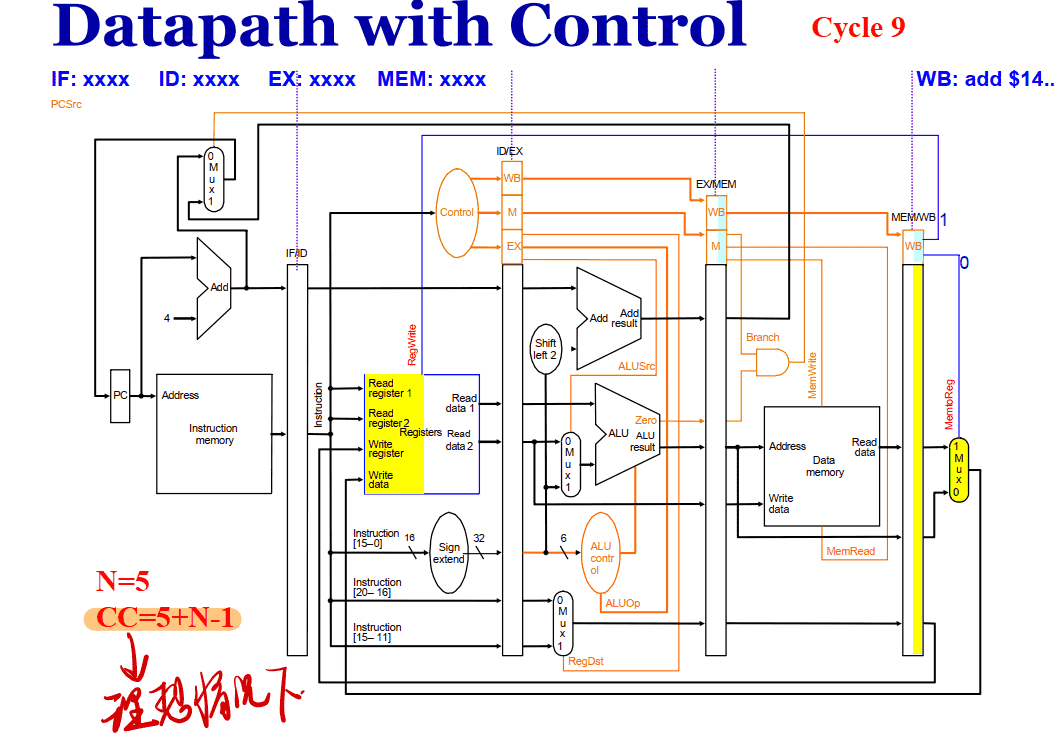

Datapath with Control

PPT第45页

Stage Control

- Instruction Fetch: 总是要读取指令存储器和写⼊ 更新的PC,所以在这个流⽔线阶段没有什么特别需要控制的

- ID/RF:与前⼀阶段⼀样, 每个时钟周期都会发⽣相同的事情, 因此⽆需设置选择控制线

前两个周期是所有指令都需要的,所以没有特别需要控制的

- Execution:设置的信号是 RegDst、 ALUop/Func 和 ALUSrc。 这些信号确定指令的结果是否写⼊位 rt (20-16)(对于load) 或 rd(15-11)(对于 R 格式) 寄存器, 并指定 ALU 操作, 确定 ALU 的第⼆个操作数是寄存器还是符号扩展⽴即数

- Memory Stage: 这个阶段设置的控制线是Branch、 MemRead和MemWrite。这些信号分别为 BEQ、 LW 和 SW 指令设置

- WriteBack: 两条控制线分别是 RegWrite 和 MemToReg, 决定写⼊寄存器数据是ALU 结果还是内存值

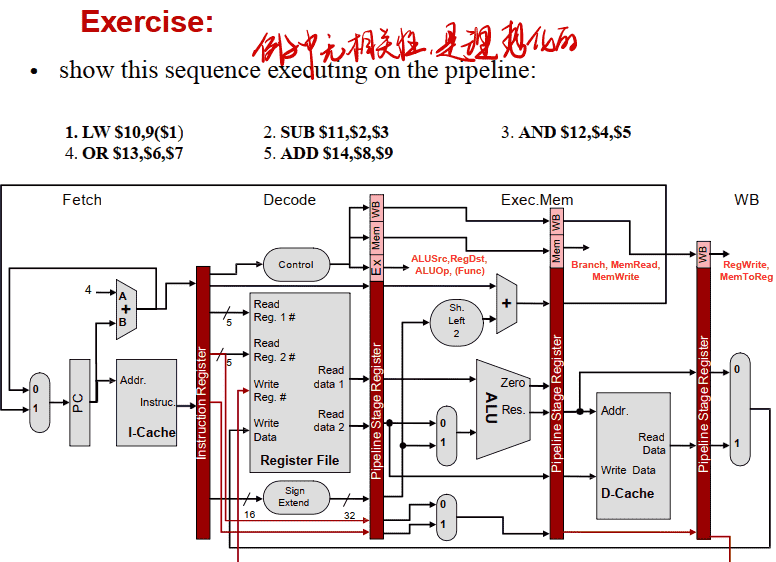

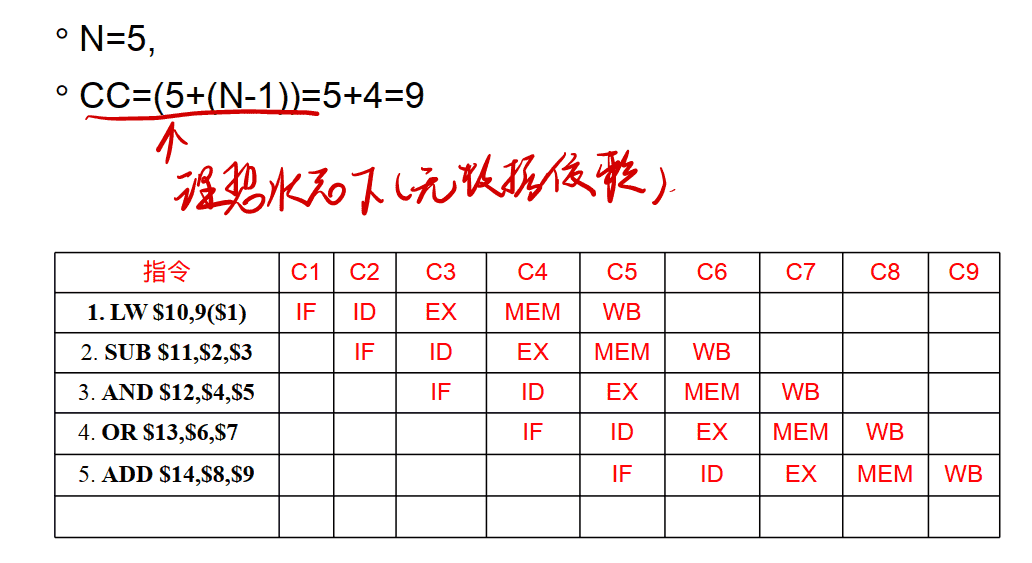

例子

分析:所需周期数为4+N=4+5=9

Cycle 1

Cycle 2

Cycle 3

Cycle 4

Cycle 5

Cycle 6

Cycle 7

Cycle 8

Cycle 9

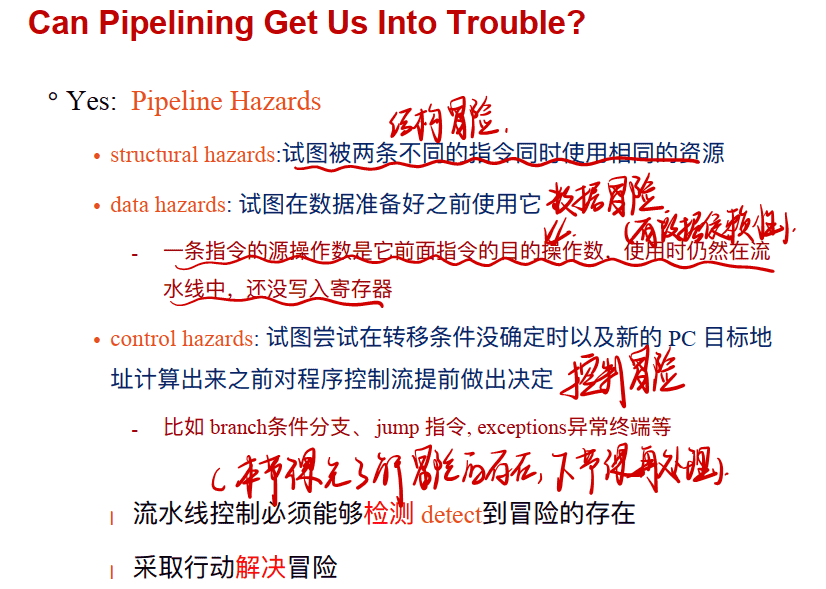

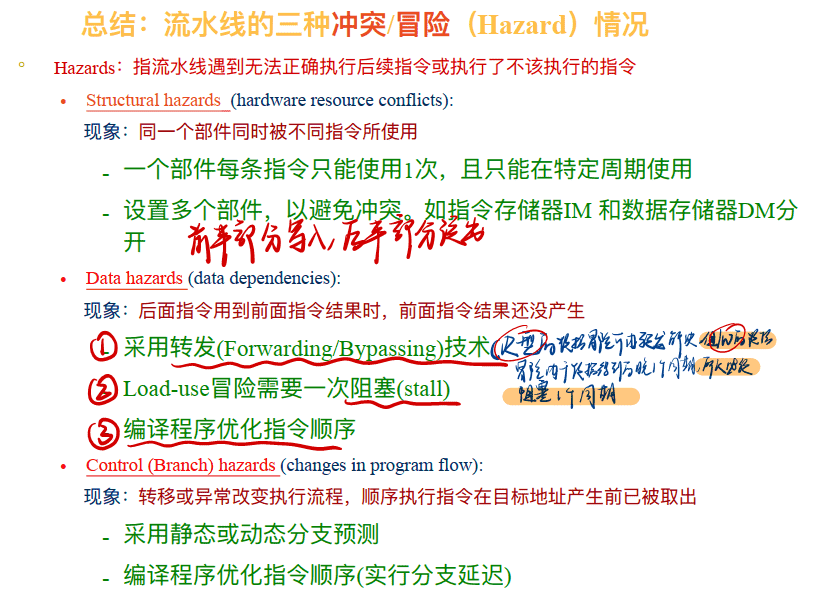

流水线存在问题

- 结构冒险:试图被两条不同的指令同时使⽤相同的资源

- 数据冒险:试图在数据准备好之前使⽤它

- 控制冒险:试图尝试在转移条件没确定时以及新的 PC ⽬标地址计算出来之前对程序控制流提前做出决定

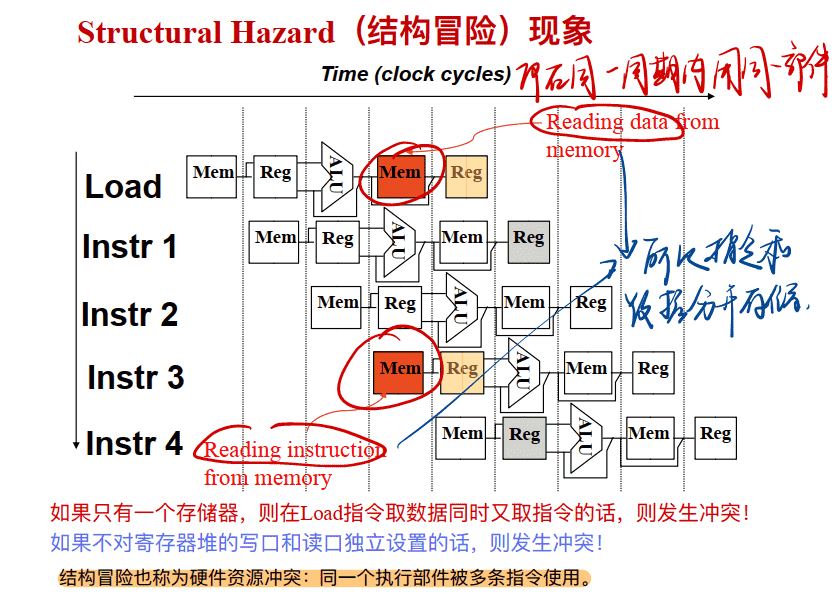

Structural Hazard(结构冒险) 现象

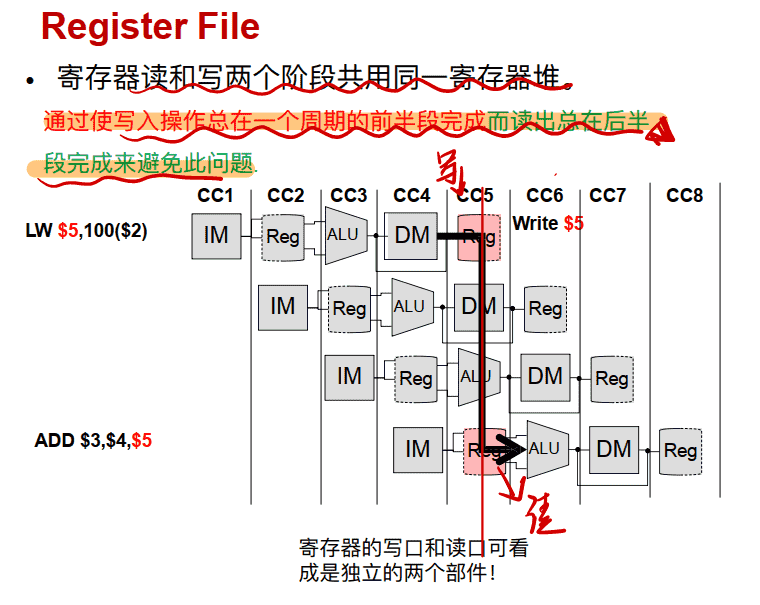

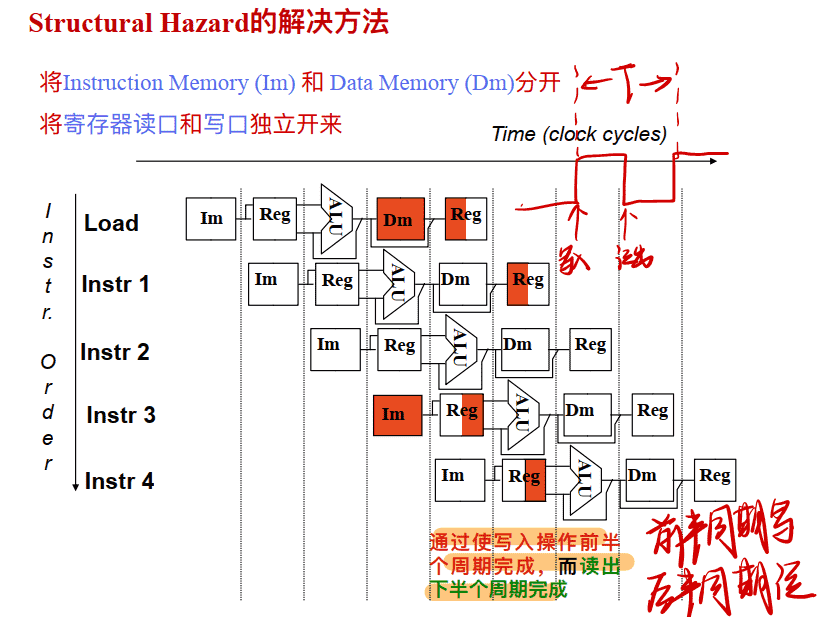

Structural Hazard的解决方法

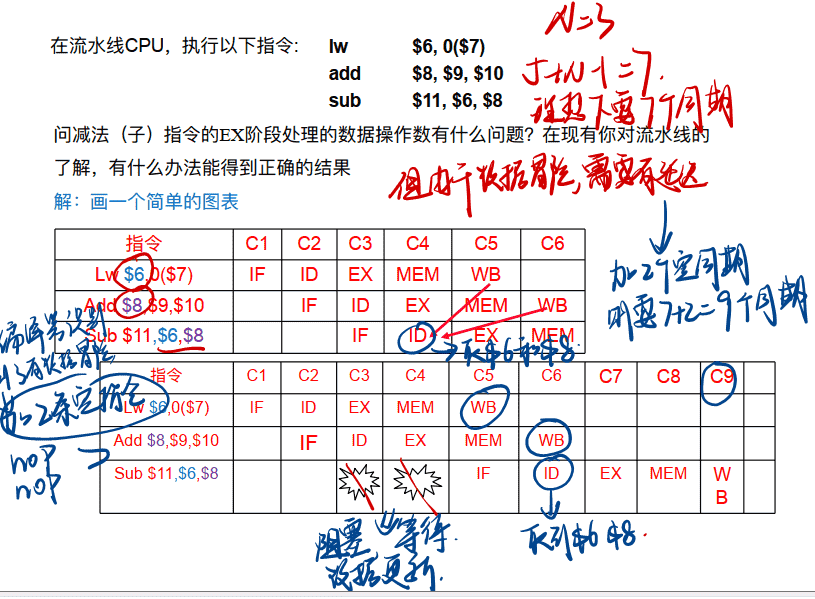

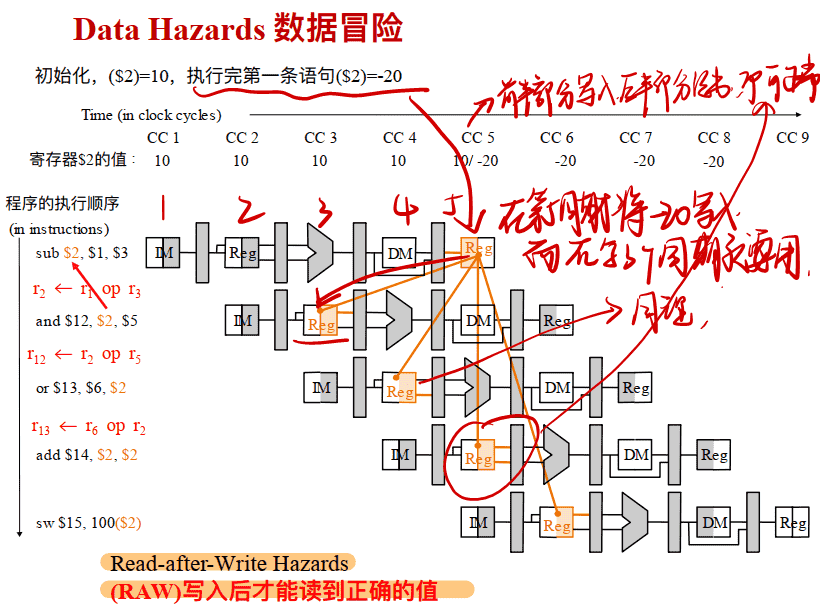

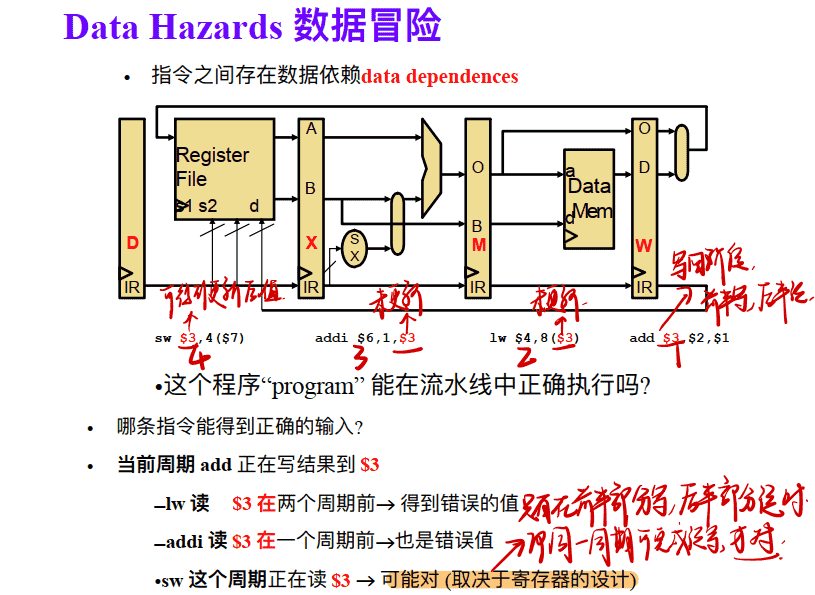

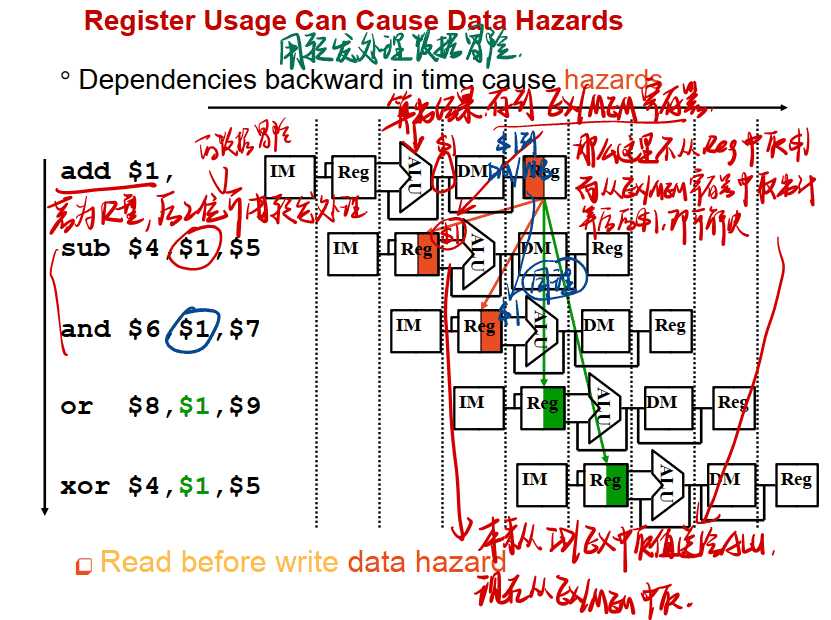

Data Hazards 数据冒险

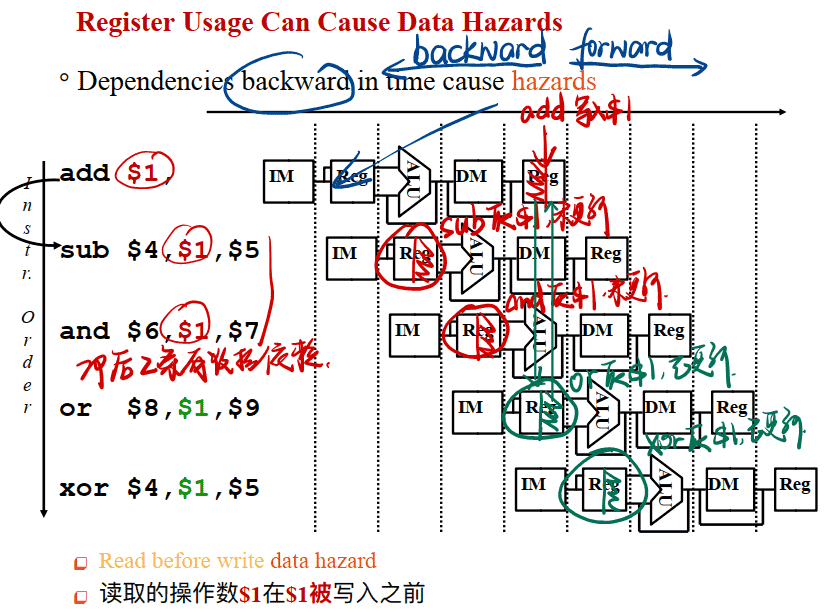

Register Usage Can Cause Data Hazards

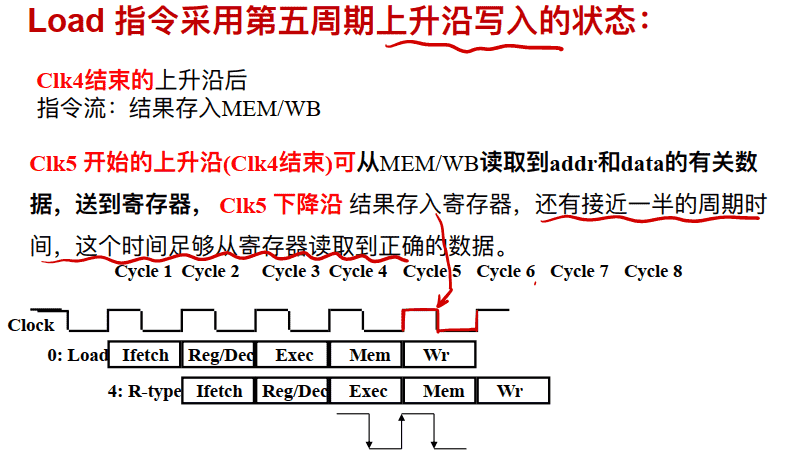

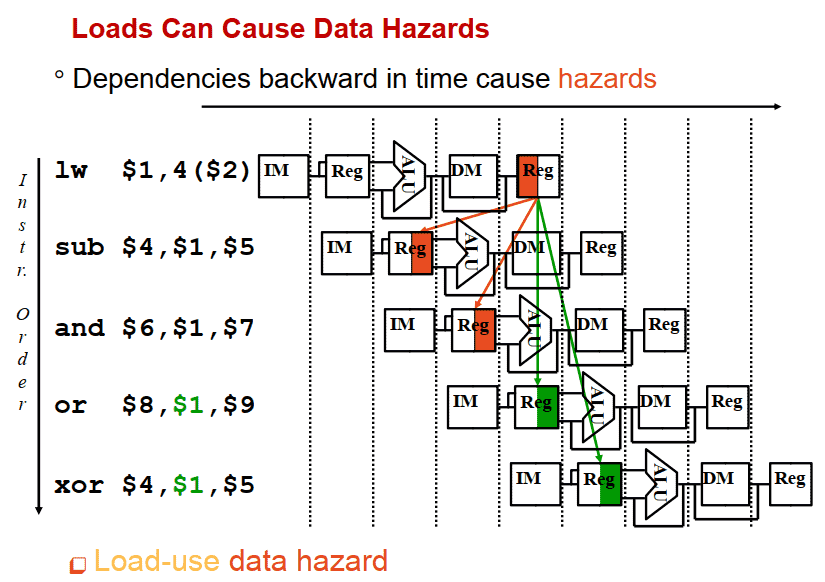

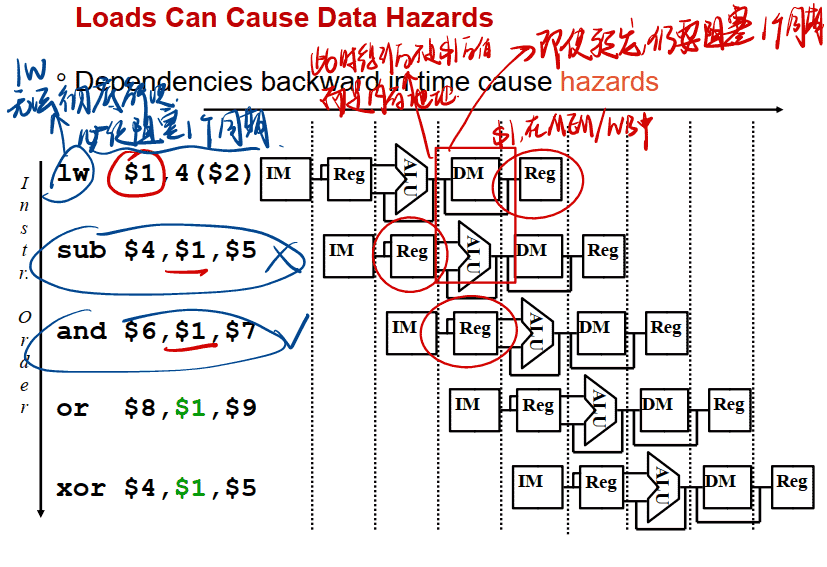

Loads Can Cause Data Hazards

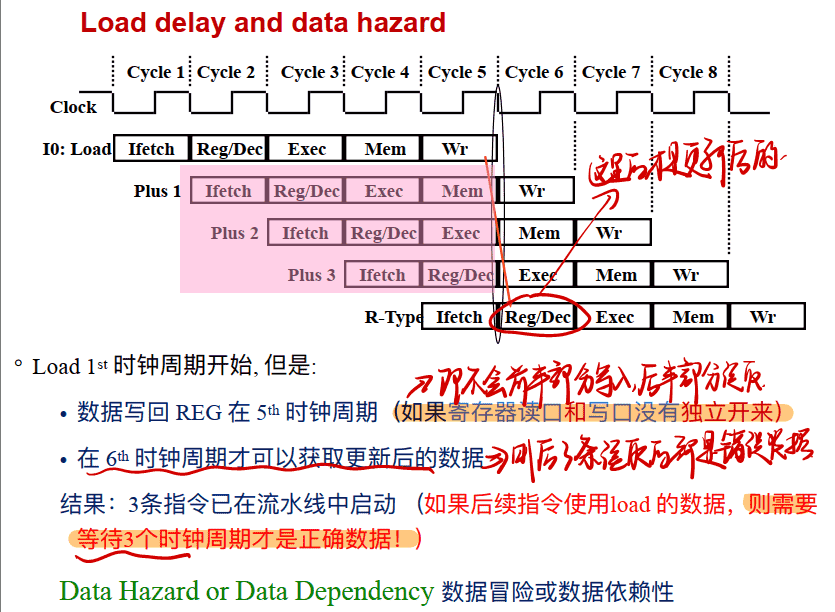

Load delay and data hazard (此时对寄存器操作的阶段ID和WB无前半段写入,后半段读取规定)

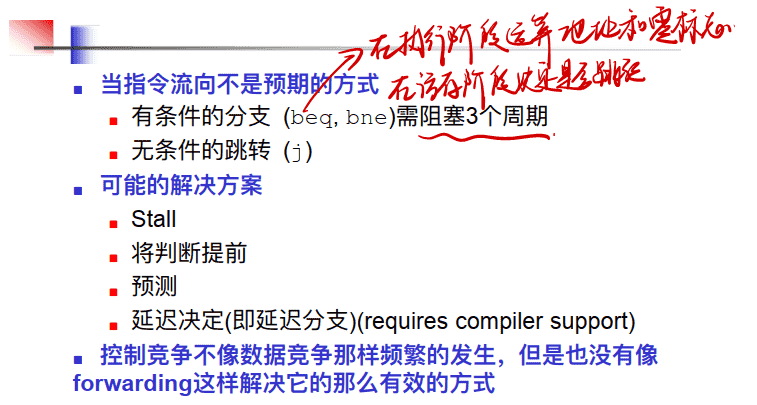

Control Hazards控制竞争

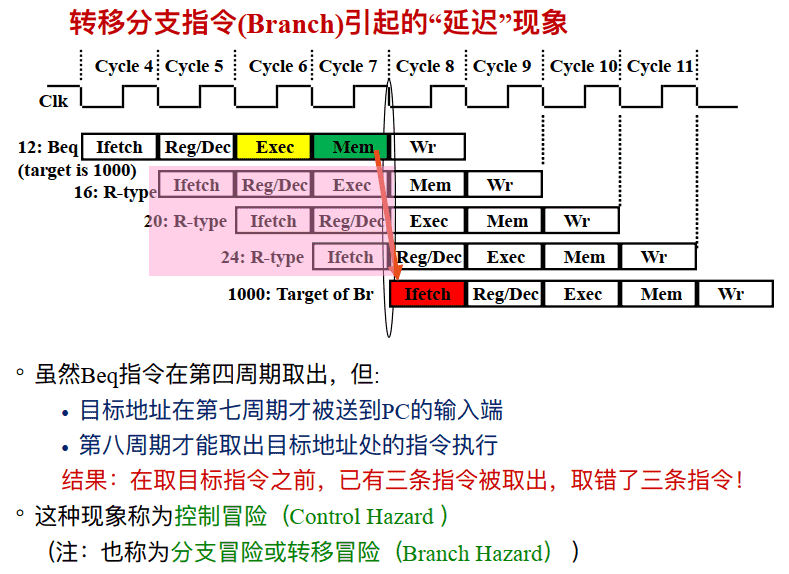

branch流水线执行过程和转移分支指令(Branch)引起的“延迟”现象

即本来应该是要跳转到其他指令的,

了

总结: 流水线的三种冲突/冒险(Hazard) 情况

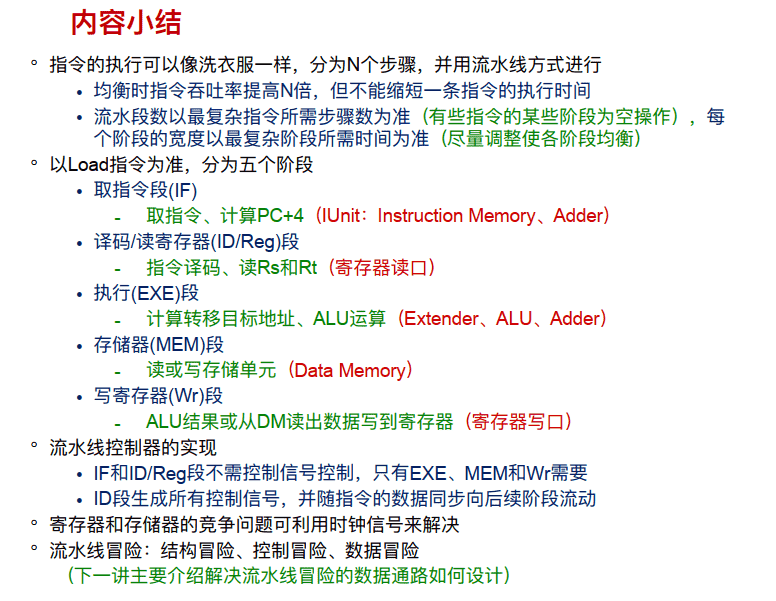

内容小结

- 指令的执⾏可以像洗⾐服⼀样, 分为N个步骤, 并⽤流⽔线⽅式进⾏

- 均衡时指令吞吐率提⾼N倍, 但不能缩短⼀条指令的执⾏时间

- 流⽔段数以最复杂指令所需步骤数为准(有些指令的某些阶段为空操作) , 每个阶段的宽度以最复杂阶段所需时间为准(尽量调整使各阶段均衡)

- 以Load指令为准, 分为五个阶段

- 取指令段(IF) - 取指令、 计算PC+4(IUnit: Instruction Memory、 Adder)

- 译码/读寄存器(ID/Reg)段 - 指令译码、 读Rs和Rt(寄存器读⼝)

- 执⾏(EXE)段 - 计算转移⽬标地址、 ALU运算(Extender、 ALU、 Adder)

- 存储器(MEM)段 - 读或写存储单元(Data Memory)

- 写寄存器(Wr)段 - ALU结果或从DM读出数据写到寄存器(寄存器写⼝)

- 流⽔线控制器的实现

- IF和ID/Reg段不需控制信号控制, 只有EXE、 MEM和Wr需要

- ID段⽣成所有控制信号, 并随指令的数据同步向后续阶段流动

- 寄存器和存储器的竞争问题可利⽤时钟信号来解决

- 流⽔线冒险: 结构冒险、 控制冒险、 数据冒险 (下⼀讲主要介绍解决流⽔线冒险的数据通路如何设计)

例子:单周期和流水线对比

==易错点:流水线的时钟周期除了五个阶段中最长的阶段所需时间外,还又CLK-to-Q time 和 setup time==